# 초저전력 미래반도체 기술개발사업 기획연구

(Study on the strategy to develop extreme low power future semiconductor technology)

연구기관 : 광주과학기술원

2017. 4. 13.

미래창조과학부

# 안 내 문

본 연구보고서에 기재된 내용들은 연구책임자의 개인적 견해이며 미래창조과학부의 공식견해가 아님을 알려드립니다.

미래창조과학부 장관 최 양 희

# 제 출 문

미 래 창 조 과 학 부 장 관 귀하

본 보고서를 **"초저전력 미래반도체 개발사업 예타기획 연구"**에 관한 최종보고서로 제출합니다.

2017. 04 . 13.

# 목 차

| 요 약 문                       | 1   |

|-----------------------------|-----|

| 1. 사업기획의 개요                 | 32  |

| 2. 국내외 환경분석                 | 41  |

| 2.1 초저전력 ICT 산업 동향          | 41  |

| 2.2 초저전력 ICT 연구 개발 동향       | 47  |

| 2.3 초저전력 ICT 분야 특허동향        | 57  |

| 2.4 해외 주요국 반도체 분야 R&D 정책 동향 | 63  |

| 3. 국내 R&D 역량분석              | 71  |

| 3.1 초절전 미래반도체 분야 R&D 현황     | 71  |

| 3.2 초절전 ICT 분야 국내 R&D 역량    | 75  |

| 4. 사업의 개념 및 목표              | 79  |

| 4.1 사업의 개념                  | 79  |

| 4.2 비전 및 목표                 | 81  |

| 4.3 추진전략 및 특징               | 83  |

| 4.4 상위계획과의 관련성              | 85  |

| 4.5 기대효과                    | 89  |

| 5. 사업 내용 및 투자 계획            | 93  |

| 5.1 사업 범위 및 세부 내용 도출        | 93  |

| 5.2 초저전력 기술 로드맵 구축          | 104 |

| 5.3 Top down 사업내용 및 연구계획    | 106 |

| 5.4 투자계획                    | 182 |

| 5.5 재원조달방안                  | 185 |

| 6. 사업 운영방안                | 186 |

|---------------------------|-----|

| 6.1 사업 추진 체계              | 186 |

| 6.2 사업운영범위                | 191 |

| 6.3 과제선정 및 연차평가시스템        | 197 |

| 6.4 사업 후 관리 및 연구성과 확산 방안  | 201 |

| 7. 타당성분석                  | 209 |

| 7.1 정책적 타당성 분석            | 209 |

| 7.2 정책대안에 대한 타당성분석        | 220 |

| 7.3 비용효과 분석               | 221 |

| 8. 연구원 구성 및 전문가 활용현황결과 보고 | 224 |

부록 1 7대 소자원천기술 수요조사/공청회 결과요약 및 상세보고서 부록 2 해외사업단 운영구조 사례분석 부록 3 해외주요연구프로그램 call for proposal 부록 4 경제성평가 분석보고서 부록 5 장비구축계획서

## 요 약 문

### 1.1 추진배경 및 필요성

- ICT 기술이 발전함에 따라, 정보처리기기에서 소요되는 에너지의 총량이 기하급수적으로 증가될 것으로 전망됨

- 사물인터넷 도입에 의해 스마트 홈, 스마트그리드, 스마트 카, ubiquitous health care, 동영상등에서 발생되는 정보처리 수요 폭증예상 (최대 백만배까지 증가)

- 이에 따른 데이터의 전송, 연산, 응용에 엄청난 에너지가 소모될 것으로 생각됨 (2013년 전세계 데이터센터 운영에 쓰인 전력 총량은 원자력발전소 27기의 발전용량에 해당함. 매 5년마다 2배이상, 또는 그 이상 증가하는 전력소모를 충당하기위한 발전소 건설은 불가능함)

- 대표적인 데이터센터의 경우, 국내에서도 2012년 전체 전력의 2%에서 2015년 8%로 사용량이 증가할 것으로 추정됨.

○ 미국의 경우, 2025년에는 개인용 IT기기에서의 사용량을 포함하면, 전체 에너지 생산량의 12~15%가 정보 처리에 사용될 것으로 추정됨

< 미국의 정보처리에 사용되는 에너지량>

|            | 2002 | 2020   |

|------------|------|--------|

| Digital 기기 | 13%  | 50%    |

| 정보기기       | 3-4% | 12-15% |

- C.W.Gellings, IEEE Power Eng. Rev., 1, P.15, 2002.

- 현재의 컴퓨팅 기술체계로는 미래 에너지 수요를 감당할 수 없기 때문에, 소자, 아키텍쳐, 시스템 등 전 분야에 걸쳐 초절전 연산체계로의 패러다임 전환이 필요하고, 가장 기본이 되는 신소자기술 개발이 선행되어야함

- 미세화 기술의 한계를 극복하고, 초저전력 컴퓨팅기술을 구현할 수 있는 차세대 로직소자 및 연산기술 개발경쟁이 본격화되고 있으나, 획기적인 기술발전의 계기를 마련하지 못한 상태임

- 미래 ICT 기반산업에서의 선도적 위치를 유지하고 경쟁에서 뒤처지지 않기 위해서는 차세대 혁신소자기술의 개념을 조기에 도출/검증하고, 이를 기반으로 광범위한 지적재산권 보호망을 선점한 후, 시장지배력을 확보하는 것을 최우선으로 하는 대책수립이 시급함

- 차세대 반도체 기술은 사물인터넷, 유비쿼터스화된 정보처리에 적합하도록 초저전

력 연산 체계를 지원할 수 있는 기술이 필요하다는 점에는 개략적인 공감대가 형성 되어 있으나, ITRS 등 기존 로드맵이나 IMEC 등 기술 컨소시움들도 구체적인 소 자기술, 아키텍쳐에 대해서는 개발방향을 제대로 제시하지 못하고 있음

- 최근 팹리스의 등장으로 반도체 분야의 R&D 투자가 감소되고, 반도체 주생산국 간의 기술장벽이 높아지게 되면서 미래기술동향 예측이 더욱 어려워짐

- 2020년대 후반경 도입될 신개념 정보소자기술분야는 해외 선진 업체 주도에 의해 형성된 기존의 market에 국내 반도체 산업이 공정 최적화를 통해 진입했던 기존의 방식과 달리 경쟁국가들도 기술적 우위를 확보하지 못한 초기 상태이므로, 집중적 인 연구 개발을 통한 기술주도권 확보가 가능함

- 이를 위해 지금까지의 추격형 연구와는 달리, 패러다임 전환기 이후 반도체 및 나 노전자기술 분야에서의 주도권을 선점하는 것을 목표로 하는 도전적인 연구개발 지 원/추진 전략을 수립하는 것이 매우 시급함

- 차세대 ICT 기기 (사물 인터넷, 스마트폰, 스마트 위치등 웨어러블 기기, 임플랜터블 기기, 초절전 고성능서버, 데이터센터 등)와 관련된 미래산업 경쟁력은 초저전력 미래반도체 기술이 결정하게 될 것임

### ■ 선진국들의 대응현황

- IBM은 2014년 CMOS 기술시대의 종말을 예측하고, 물리적 미세화 없이도 낮은 전압에서 동작하는 초저전력, 고성능 연산 기술 개발을 선언함

- 이를 기점으로 7nm 이후 미세화의 한계를 극복하면서도, 차세대 ICT 기술 (스마트폰, 스마트 위치, 접는 노트북 등)에 적용 가능한 신개념 반도체 소자 원천기술 선점을 위한 본격 경쟁이 시작되었으며, 미국, 유럽, 일본 등에서는 차세대 미세화 기술은 물론 미세화를 필요로 하지 않는 새로운 형태의 정보처리기술을 개발하기 위해 대형 중장기 연구프로그램들을 다수 운영 중임

- 미국은 정부 주도로 차세대 소자 및 시스템 기술개발에 본격적으로 나서고 있음

- 2016년 "Energy efficient computing for devices and architectures (E2DCA)" 프로그램을 시작, 5개의 center를 중심으로 연구시작. 초절전 반도체 신소자 기술과 아키텍쳐에 대한 연구 프로그램임 (∼100억/년, 5년 투자)

- 보다 광범위한 차세대 소자 및 시스템 연구를 위해 joint university microelectronics program (JUMP)를 2018년부터 정부, 민간 공동투자로 추진예정임 (~550억/년, 6년 투자)

- 유럽은 "ICT-31: nanoelectronics and microelectronics" 연구 프로그램을 2017년 1월에 시작할 예정임 (5.4M 유로/년)

- 3차원 집적기술, 뉴로모픽 아키텍쳐 등 전력절감형 기술에 대한 연구 프로그램임.

- 그 외에도 TSV/M3M 등 소자 융합과 저전력을 위한 연구프로그램을 동시에 진행하고 있으며, 초저전력 시스템 구현을 위해 연산 아키텍쳐/회로/소자/소재에 대한 초대형 연구프로그램을 시작함

- Qualcomm-LETI(프)-SMIC(중)-북경대 등 공동개발 진행

- 뉴로모픽 소자기술의 경우 미, EU, 일본을 합쳐 2조원 정도가 투자되고 있음

- 대한민국 반도체기술 R&D 현황

- 우리 나라는 미세화 기반 공정기술에서의 우세를 바탕으로 시장을 확보해왔음

- 국내 주요 반도체 기업인 삼성과 SK 하이닉스는 미세화 공정 및 메모리 분야에서는 강세를 보이나, 그외의 미래기술에 대해서는 체계적 대응전략이 미흡한 상황임

- 국내 산업계가 주로 이용해온 IBM alliance, SEMATECH\*, IMEC 등의 기술도입 선이 기술개발을 포기하거나, 매우 부진한 상황이어서, 독자기술개발의 필요성이 대두되고 있음

- \* SEMATECH: 삼성, Intel등 반도체기업들이 공동으로 자금을 출연, 기초연구를 수행하는 기관, 1983년 설립, 2015년 뉴욕주 소재 CNSE에 합병된 후 폐업상태임

- 초저전력 융합 소자, IoT 등 4차 산업혁명을 이끄는 기술에 기반한 초연결 사회에 대비한 기반 연구는 매우 부족함

- 뉴로모픽 소자기술은 미래융합파이오니어 사업에서 일부 진행 중

- 산업부 미래소자원천기술개발사업 (총 사업비 1000억, '13-'21)이 시작되었으나, 5년이내 상용화가 가능한 단기 R&D 과제 중심으로 운영되고 있음

- 현 정부의 나노전자소자 관련 R&D 투자는 중기과제대비 (38%) 대비 장기 나노 분야 기술과제(42%)에 대한 비중이 높았는데, 이것은 전자소자 분야에서 대기업의 역할이 강조되면서, 학술적인 가치가 다소 적지만, 상용화가능성이 있는 나노전자 기술에 대한 지원이 매우 제한적이었기 때문인 것으로 분석됨

- 차세대 시스템관련 연구로 지능형반도체 사업이 추진되고 있으나, 현재 사용중인 CMOS소자기술에 기반하여, 시스템 성능을 고도화 하는 방식의 연구여서, 차세대 패러다임 전환기술개발에 필요한 혁신기술 연구는 추진되지 않고 있는 상태임

- 이 추세가 지속된다면, 우리나라의 기간산업인 반도체, 디스플레이 등 전자산업이 경쟁력을 상실하게 되고, 중국에 추월당하게 되는 것은 시간문제임

- 미국에서 반도체 제조가 퇴조하고, 연구지원에 축소되면서 R&D outsourcing이 확대되고 있으나, 반도체 분야에서의 국제공동연구 파트너로 한국이 아니라 유럽, 대만, 중국이 선호되고 있음

- 중국은 전세계에 퍼져있는 화교인력을 기반으로 중국 내의 연구역량을 급속히 발전시켜나가고 있으며, 이러한 추세에 기인함

- 초저전력 미래 반도체 기술 선점을 위해 아키텍쳐/회로/소자/소재 기술을 연결하는 계층통합형 중장기 연구프로그램이 필요함

- 현재의 반도체 기술은 향후 6년이내에 cost-performance cross over\*가 일어날 것으로 예측됨

- \*cost-performance cross over: 차세대 기술 사용비용이 그에 따른 이익을 초과하는 현상

- 시스템 성능을 향상시키기 위해 필요한 비용을 억제하면서도 초저전력 시스템을 구성하기 위해 현재와는 전혀 새로운 반도체소자 및 활용 아키텍쳐 기술이 필요해짐

- 아키텍쳐/회로/소자/소재 반도체 전 분야 연구자들이 모여 초저전력 반도체 기술 개발이라는 목표를 조기 달성하기 위해 집중적인 연구가 필요

- 차세대 ICT 기반 부품, 소재, 장비등 광범위한 산업분야에서 선도기술 선점가능

### 1.2 사업의 개요

■ 사업의 비전 및 목표

그림 1. 사업의 비전 및 목표

### ■ 사업의 목적

○ 국가 기간산업인 반도체 산업의 미래 기술경쟁력 확보를 위해, 국내 민간기업들이 미처 대응하지 못하고 있는 초저전력 미래반도체 원천기술을 정부주도로 개발하여, 차세대 반도체 산업의 글로벌 기술경쟁력을 확보하는 것을 목적으로 하는 사업

### ■ 사업의 성격

- 국가산업의 미래경쟁력을 제고하고 궁극적으로 국민의 삶의 질을 향상시킬 수 있는 창조혁신형 기초원천 연구개발사업

- 원천특허를 확보하여 사업 후 응용개발, 실용화 개발까지 연계가 가능한 사업

- 반도체산업의 기술 패러다임 전환기에 글로벌 기술리더쉽을 확립하여, 차세대 기술 개발 및 사업화 주도권을 확보함으로써, 전후방 파급효과를 강화하고, 민간기업의 적극적인 참여를 유도하하여 정부투자효율을 극대화하는 새로운 사업모델

### ■ 사업의 핵심적 특징

- 본 사업은 10년간 총 4,000억원 (연평균 400억원, 정부예산 2,800억, 민간투자 1,200억)이 투입되도록 설계되어 단일 목표를 가진 사업으로는 최상위 그룹에 속하는 장기 대형 국가연구개발 사업임

- 소자기술을 중심으로 소재, 공정, 집적기술은 물론 설계, 아키텍쳐까지 종래 순차적으로 개발되어온 기술을 CAD기술의 발전을 기반으로 병렬로 개발하는 사업구조임

- 짧은 시간내에 선도적 기술을 개발하기 위해서는 종래의 R&D 방식을 탈피하여, 혁신적이고 도전적인 기술개발 체계를 도입해야함

- 본 사업에서는 아래와 같은 방식으로 소자기술에서 시스템설계기술까지의 개발기간을 최대한 단축함으로써, 경쟁국대비 압도적인 기술 경쟁력을 확보하고, 선직국 대비 열세인 설계기술분야의 도약적발전을 달성하고자 함

- 소자기술의 개발, 검증기간동안 이상적인 소자모델을 적용한 설계 및 아키텍쳐 연구를 병행하고, 점진적으로 이상적인 모델을 현실적인 모델로 바꿔나가면서 시스템 설계 기술의 완성도를 제고함

- 국가 나노인프라시설을 적극적으로 활용, 국내 학계의 소자 및 공정 연구수준을 획기적으로 제고함. 이를 위해 사업단과 나노인프라 기관간의 밀접한 협력체계를 구축함

- 소자,공정등 플랫폼 기술개발 부문의 개발리스크를 줄이고 투자효율을 높이기위해 해외 유사 연구프로그램과의 적극적 네트웍을 구성하며, 민간자본을 유치할 수 있 는 수준까지 기술의 성숙도를 높임

- CAD 기반기술의 해외의존을 탈피하고, 자체 설계 시스템을 개발, 설계 IP를 확보 함으로써, 반도체 산업의 고질적인 문제점인 설계 기술 경쟁력을 제고함

- 소자에서 시스템설계까지의 개발과정을 단일사업단으로 총괄관리함으로써 개별사업에서 발생할 수 있는 협력부재, 융합기술 부재등의 문제점을 극복함

- 글로벌 오픈이노베이션 체계를 활용하고, 나아가 글로벌컨소시움을 한국주도로 결성하여, 글로벌 기술리더쉽을 확보하는 것을 목적으로 하는 사업임

- 1단계에서는 국내 R&D 역량이 부족한 분야에 국내외 전문가를 적극적으로 활용 함.

- 1단계 기간동안, 유사기술분야 해외 R&D 프로그램과의 적극적인 네트웍 구축, 국 내외 민간기업들의 observer형태의 참여로 2단계 민간투자 유치 기반구축 (반도체 연구는 연구결과가 상품화되는 것이 아니라, 연구프로그램이 상품화되어 투자를 유치하는 방식이므로, 미래 반도체산업에 필요한 연구목표를 잘 설정하고, 실행계획을 세우면, 투자유치가 가능함)

- 2단계에서는 기술이전, 국내 민간기업의 매칭등의 방법으로 연구컨소시움을 구성하여, 정부투자의 ROI (return on investment)를 극대화함

- 3단계에서는 해외 기업을 포함한 민간기업이 참여하는 상용화 연구에 중점을 두고, 1-2단계의 성과를 적극 활용하면서, 팹리스 창업등 사업단의 성과를 극대화함

#### ■ 상위계획과의 관련성

| 상위계획                | 관련항목                                              | 관련성이 높은 항목             | 본 사업과의 부합성                                                           |

|---------------------|---------------------------------------------------|------------------------|----------------------------------------------------------------------|

| 제3차<br>과학기술기본<br>계획 | • High2: 국가전략<br>기술개발 -<br>5대추진분야(IT융<br>합 신산업창출) | • CPND기반 ICT<br>혁신역량강화 | 지 능 형 반 도 체 , 자율주행자동차, 인공지능, 수퍼컴퓨터등에 소모되는 전력을 획기적으로 저감하여, 기술경쟁력을 제고함 |

|                                         | • | High3: 중장기               | •        | 전략분야국제공동연                | 글로벌 정부 R&D 네트웍         |

|-----------------------------------------|---|--------------------------|----------|--------------------------|------------------------|

|                                         |   | 창의역량강화(과학                |          | 구활성화                     | 구축 (1단계), 글로벌          |

|                                         |   | 기술 글로벌화)                 |          |                          | R&D 컨소시움 구축            |

|                                         |   |                          |          |                          | (2단계)을 통해              |

|                                         |   |                          |          |                          | 미래반도체분야 공동연구           |

|                                         |   |                          | •        | 국제과학기술허브구                | 활성화                    |

|                                         |   |                          |          | 축                        | 초저전력 미래반도체 R&D         |

|                                         |   |                          |          |                          | 컨소시움의 본부를 한국에          |

|                                         |   |                          | •        | 국제협력                     | 설치하여, 기술리더쉽            |

|                                         |   |                          |          | 인프라조성                    | 확보                     |

|                                         |   |                          |          |                          | 국 내 외                  |

|                                         | • | High4: 신산업               | •        | 지식재산활용촉진                 | 나 노 인 프 라 기 관 들 을      |

|                                         |   | 창출지원(기술이전/               |          |                          | 연결하여 공동연구가             |

|                                         |   | 사업화촉진)                   |          |                          | 가능한 인프라구축              |

|                                         |   |                          |          |                          | 2단계 사업진입시 1단계          |

|                                         |   |                          |          |                          | 정부투자에 의해 발생된           |

|                                         |   |                          |          |                          | 지적재산권을 package         |

|                                         |   |                          |          |                          | 형태로 이전하는 새로운           |

|                                         |   |                          |          |                          | 형태의 기술이전 방식            |

| 2                                       |   |                          |          | 1. 6 7 7 2 2 2 2         | 도입                     |

| M47                                     | • | 전략 1: 혁신주도               | •        | 나노융합확산인프라                |                        |

| 나노기술종합                                  |   | 나노산업화 확산                 |          | 강화 - 차세대                 | 집적공정개발에 연계할            |

| 발전계획                                    |   |                          |          | 초절전 집적기술                 | 계획임                    |

|                                         |   | 7) 7} O.                 |          | 플랫폼개발                    | 본 기획은 해당 사업의           |

|                                         | • | 전략 2:                    | •        | 4대                       | 실행을 위해 수행된             |

|                                         |   | 미래선도기술확보                 |          | 나노챌린지기술 -                | 과제임                    |

|                                         |   |                          |          | 초저전력<br>미계비드레            |                        |

| 계 1 기 기 기 기 기 기 기 기 기 기 기 기 기 기 기 기 기 기 | - | 지역R&D 투자 특성              | •        | 미래반도체<br>특화산업분야 지정·      | 나노이 프리지션에서             |

| 세4차 시방파<br> 학기술진흥종                      | 1 | 지역K&D 구사 즉성<br>화·내실화'특구별 |          | 극와산업군아 시성·<br>육성 - 선행공정개 |                        |

| 악기물신응공<br> 합계                           |   | 자'네결과 국무절                |          | 파성 - 신행공성개<br>발사업        | /개월선<br>선행플랫폼공정들을 본    |

| [월계                                     |   |                          |          | 三八.月                     | 사업의 집적공정개발에            |

|                                         |   |                          |          |                          | 사업의 접적등정개절에<br>연계할 계획임 |

|                                         |   |                          | <u> </u> |                          | 신계된 계측 급               |

### 1.3. 초절전 ICT 기술개발 전략

### ■ 핵심 과제 도출 전략

- 반도체 소자의 소모전력을 획기적으로 저감하는 데 기여할 수 있는 소자기술로서, 5년이내에 상용화 가능성을 검증하고, 10-15년이내에 상용화제품에 적용이 가능한 중장기 연구대상 기술을 중심으로 전문가들 대상 및 기획팀 자체 기술조사를 통해 topw down 신소자 기술을 도출함. 이와 동시에 다양한 소자개발 목표를 구체화하여 bottom -up 신소자 기술 아이디어를 수용할 수 있는 형태로 과제 도출

- 상기 기준에서 벗어나는 단기연구과제 (예시: III-V, GE MOSFET), 또는 초장기 연구과제 (예시: 스핀로직)가 필요한 기술은 제외함

- 연산 소자기술의 초저전력화에 기여할 수 있는 기술로 범위 제한 (예시: 전력반도

체등 제외)

- 위의 과정을 통해 도출된 기술을 상용화 하기위해 필요한 단위공정, 집적공정을 개발하기위한 과제, 신기술을 적용한 중규모 집적칩을 제작하기위한 나노인프라 보완투자를 위한 과제를 도출하는 플랫폼 기술개발 프로그램 도출

- 신소자 기술개발과 병행하여 신소자기술을 적용한 회로를 설계하고, 집적회로 설계기반을 구축하는 과제, 최종적으로 신소자기술을 적용한 시제품 칩을 제작하는 수준의 상용화과제를 플랫폼기술개발 프로그램과 상호연계가 가능한 형태로 구성한 시스템집적기술개발 프로그램 도출

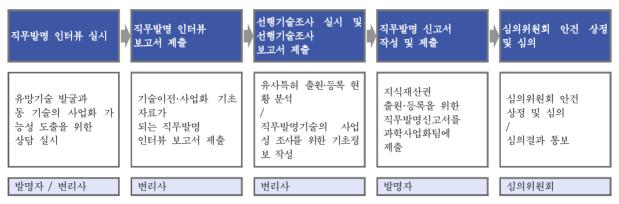

### ■ 사업 추진 구조

○ 앞 절에서 제시한 과제 및 프로그램간의 상호연관 체계는 다음과 같음

그림 2 과제간 연계 구조

- 선행공정 플랫폼사업과 소자개발시범사업은 2015년, 2016년에 시작된 과제들로서, 본 사업의 시범사업의 성격을 가지고 있음

- 글로벌 오픈이노베이션과제는 한-EU정부가 협의된 국제협력 프로그램을 수용하고, 국내전문가가 부족하여 해외전문가들의 참여가 필요한 분야를 공동개발하기위한 과제임.

### ■ 총괄사업 로드맵

- 본 과제는 초기 기술 검증 (1단계), 시제품 개발(2단계), 시스템 개발 (3단계) 등 3단계로 구분하여 추진됨

- -본 사업은 기존의 CMOS기술을 활용하면서, 신소자기술을 BEOL 부분에 추가하 여, 전체 소모전력을 감소하는 방식을 기반으로 하고 있음.

- 여러 가지 기술을 조합하여, 1/10, 1/100, 1/1000의 목표를 달성할 수 있기 때문 에, 개별소자기술로 달성할 수 있는 최대 목표치를 제시하는 것으로 총괄목표 설 정에 대한 수치적 근거제시를 대신했음. 각 기술별 소모전력 절감목표는 아래 총 괄 기술로드맴에 제시되어 있음.

- 절감목표가 높을 수로 여러기술이 융합되어야하므로. 기술개발 난이도가 높아지 고, 응용분야도 광범위해지므로. 단계적인 시스템개발 및 상용화를 위해, 중간단계 에 해당하는 1/10, 1/100 목표를 별도로 설정하고, 이를 추구하는 하부 연구프로 그램을 별도로 제시한 것임

- 각 단계별로 핵심기술 선정, 검증작업이 진행되며, 그에 따라 예산이 조정됨. Top down 형 과제, bottom up형 과제 모두 기술개발 성과에 따라 과제 계속 여부를 결정하나, 시범사업을 수행하지 않은 bottom -up과제의 경우 1단계 종료시점에서 기술타당성을 검증할 계획임

- 정부투자비율이 단계별로 감소됨에 따라, 민간기업이 참여하는 컨소시움의 폭을 확대 해야하며, 이에 따라 예산 투입 비율이 과제별로 변동될 수 있음

- 아래 로드맵은 시제품 수준의 전력절감목표와 제품 수준의 전력절감 목표를 구분했음. 사업단은 시제품 수준의 목표를 달성하기위한 연구를 수행하지만, 2단계와 3단계에서 조기 상용화제품 연구를 하는 경우를 고려하여 목표치를 다소 보수적으로 설정했음

### ■ R&D 프로그램 세부구성

### ○ 공정/집적 플랫폼 개발 사업

그림 2. 공정/집적 플랫폼 개발 사업의 구성

- 전문가 수요조사를 통해 도출된 top down 소자원천기술(초저전압 소자, Monolithic 3D, 자기재구성 소자, 다치로직 소자, 로직-인-메모리 소자, 광배선 소자, 뉴로모픽 소자)과 향후 선발될 bottom-up 소자원천기술을 단위 소자 레벨에서 구현하고 및 array 또는 ALU 수준의 중규모 칩 집적을 위한 플랫폼 기술 개발

- 새로운 소자를 집적하기위해 필수적인 신공정기술, 장비기술등을 개발하고, 국내나노 인프라기관에 기술이전한 후 집적공정연구를 통해 중규모 집적 칩의 성능 및 수율확보

- 본 플랫폼 개발을 통해 초저전력 미래반도체 시장에 신기술 적용 주도권을 확보할 수 있으며, 단계별 상용화를 통해 원천기술 및 파생 기술의 지적 재산권을 조기에 확보.

- 참고 (top down 기술로 조사된 소자원천기술)

| top down<br>소자원천<br>기술 | 연구 분야의 정의                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 초저전압<br>소자             | <ul> <li>0.5 V 이하의 구동전압에서도 동작하며, CMOS 소자의 전력<br/>축소화를 극복할 수 있는 미래 소자 및 이러한 소자를 응용한 회로<br/>기술</li> <li>미래소자원천기술개발사업(산업부)에서 포함되어 있지 않는 신소재<br/>기반 tFET등 신소자중심의 기술연구</li> </ul>                                                                                                                                                                                                                                  |

| Monolithic<br>3D       | <ul> <li>소자가 형성된 웨이퍼상에서 새로운 소자층을 3차원 적층 후 후속소자를 형성하는 기술</li> <li>기존 3차원 기술 대비, 배선 및 마스크 개수를 줄여, 소자 밀도증가, 전력 감소, 성능 향상.</li> <li>회로 및 소자 형성 기술 flexibility 증대와 현재 fab. friendly한 기술</li> <li>M3D 기술은 제안되는 채널 형성 방법에 따라 크게 본딩 방식, 재결정 방식, 또는 에피 방식 등으로 나눌 수 있으나 아직 개념 정립단계임.</li> <li>Monolithic 3D기술의 상용화를 위해서는 여러 특수한 저온 단위공정과 함께 이들 단위 공정들을 최적으로 조합하여 초저전력을 구현할 수 있는 집적공정 및 architecture 개발이 필요함.</li> </ul> |

|           | - M3D 기술은 선행공정 플랫폼사업을 통해 기본 기술이 개발되고                                          |

|-----------|-------------------------------------------------------------------------------|

|           |                                                                               |

|           | 있으며, 본 사업에서는 집적기술개발과제에서 포괄하여 시스템                                              |

|           | 집적에 필요한 수준의 상용화기술을 개발할 계획임                                                    |

|           | - 반도체공정에 집적 가능한 나노스위치를 개발하고 기존의 2진 연산                                         |

|           | 플랫폼에 나노스위치를 집적하여 환경에 따라 기능을 유연하게 변형할                                          |

|           | 수 있게 하여 초저전력으로 확률적컴퓨팅을 구현하는 것을 목표로                                            |

|           | 하는 기술                                                                         |

|           | - 아날로그 및 디지털회로가 하나의 하드웨어로 여러 가지 기능을                                           |

| 되 키 케 그 거 | 구현될 수 있도록 산재된 나노스위치를 구비한 소자                                                   |

| 자기재구성     | - 미래소자원천기술개발사업(산업부)에서 시범사업으로 개발되는                                             |

| 소자        | 실리콘 후공정을 활용한 나노스위치 이외의 tFET 나 고성능 비휘발성                                        |

|           | 메모리 등 신소자기반의 나노스위치의 기술연구 및 자기재구성                                              |

|           | 일고리즘 연구                                                                       |

|           | - 반도체 전공정 소자와 메모리소자의 조합을 통한 재구성로직은                                            |

|           | 유연성을 증가시켜서 회로의 복잡성과 소모전력을 동시에 줄일 수                                            |

|           | 기 한경을 하기시키지 되고의 학합생의 고고한력을 하시해 말을 때<br>                                       |

|           |                                                                               |

|           |                                                                               |

|           | 복잡성, 그리고 소모 전력을 동시에 줄일 수 있는 기술                                                |

| 다치로직      | - 나노소재원천기술개발사업 (미래부)에서 시범사업으로 개발되는                                            |

|           | 저온집적소자기술을 제외한 전공정소자를 포함한 신소자기술 개발                                             |

|           | - 다치로직은 기존의 이진로직 대비, 단일 회로 면적과 회로 연결의                                         |

|           | 복잡성, 그리고 소모 전력을 동시에 줄일 수 있는 기술임.                                              |

|           | - 로직과 정보저장 모듈 간 정보전달지연과 급격하게 증가하는                                             |

|           | 파워소모를 해결할 목적으로, 로직 회로에 비 휘발성 정보저장 소자                                          |

|           | 집적기술.                                                                         |

| 로직-인-     | - 칩 면적을 낮출 수 있으며, 로직층과 메모리 층이 집적되어 있어,                                        |

| 메모리 소자    | 모듈간 정보전달 지연과 동적 파워 절감.                                                        |

| 메모디 조사    | - 가까운 미래에 DRAM 및 Embedded 메모리가 비 휘발성 소자로                                      |

|           | 대체되어, 시스템의 파워소모 감소와 성능개선이 가능할 것임.                                             |

|           | - 궁극적으로 비 휘발성 소자가 로직에 내장되어 있는 형태의                                             |

|           | 시스템구조로 전환되어 초 절전, 작은 면적, 고속 구현이 가능함.                                          |

|           | - 고집적화된 고속 저전력 데이터 전송을 위해서 전기 신호를                                             |

|           | 광신호로 바꾸어 전달 후 다시 전기신호로 변환시켜 CPU 및 메모리                                         |

| 광배선소자     | 등의 칩간 광배선 기술이 요구되고 있음.                                                        |

| ,, ,      | - 레이저, 모듈레이터, 도파로, 파장필터, 그리고 디텍터 등의 핵심                                        |

|           | 광소자들을 실리콘 기판 상에 구현하는 기술                                                       |

|           | - 기존 연산방법을 탈피하고, 저장 장치 간의 병목 현상을 해결할                                          |

|           | 목적으로, 뇌의 시냅스와 뉴런의 기능을 모방한 기술                                                  |

|           | - 뉴로모픽 컴퓨팅의 인공 신경망은 다수의 뉴런을 이용하여                                              |

|           | 기오고역 심규정의 한층 한경청는 나무의 개인을 이용하여<br>인지/학습을 수행하여, 고 효율 연산 능력과 초절전 기능.            |

| 뉴로모픽      | · 인시/막급을 구멍하여, 고 효율 선산 등억과 조절선 기능.<br>  - 뇌와 같이 복잡하고 집적도가 높은 구조의 뉴로모픽 시스템 개발을 |

|           |                                                                               |

|           | 위해선 신경동작 메커니즘에 대한 기초연구에 근거한 시냅스/뉴런을                                           |

|           | 모사한 소자/소재 개발 및 시냅스/뉴런 소자를 적용한 지능형 집적회로                                        |

|           | 개발                                                                            |

### ■ 초저전력 시스템 집적기술 개발

○ 신소자기술을 이용한 시스템을 설계하기위해서는 새로운 아키텍쳐에 대한 연구 및 이를 실제 설계로 연결시킬 수 있는 CAD 툴이 개발되어야함. 이를 위해 신소자기반 아키텍쳐 개발과제와 설계인프라개발과제가 각각 기획되었음

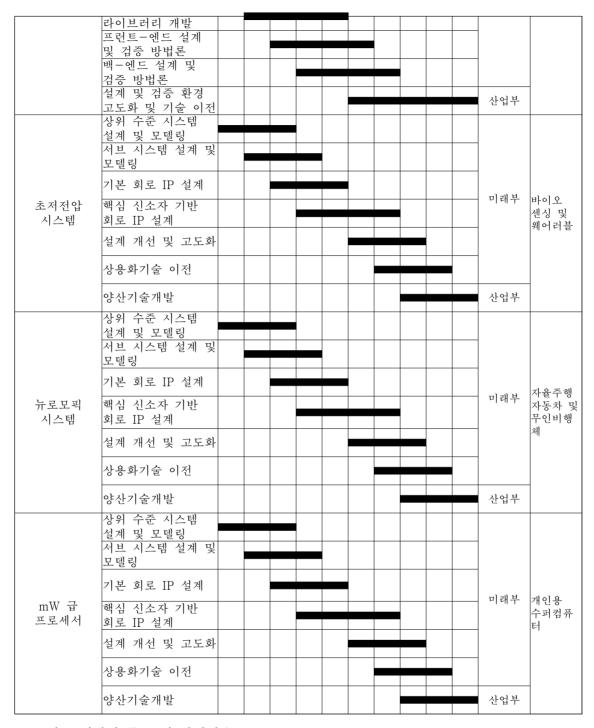

- 신소자기술을 이용한 초저전력 시스템 개발단계별로 소모전력이 점진적으로 감소됨에 따라 각각 최적 응용분야가 달라질 것으로 판단하여, 소모전력 감소율 1/10, 1/100, 1/1000에 해당하는 응용분야중 가장 중요한 분야를 전문가 수요조사를 통해 도출했음

- 이렇게 도출된 초저전압시스템, 뉴로모픽 시스템, mW 프로세서 및 파생상용화기술을 중점적으로 연구하는 과제를 구성하고, 각 과제별로 핵심기술, 응용기술, 상용화기술을 개발하는 형태로 프로그램을 개발했음

- 아키텍쳐, 설계 기술을 조기에 개발하기위해 신소자연구과제들과 긴밀한 협조체계를 구축할 계획이며, 이러한 병렬연구를 통해, 신소자기반 초저전력 미래반도체 기술의 설계 IP를 대량으로 확보하고, 이를 기반으로 기술이전, 팹리스기업창업등을 활성화함으로써, 반도체 산업의 경쟁력을 획기적으로 제고하는 것을 주요 목표로 설정했음

# 1.4. 국내외 기술개발 동향

■ 국가별 차세대 반도체 기술 개발 동향

|    | 산업현황                                                                                                                                    | 정부전략                                                                                                                                                                                                                                                 | 기술수준                                                                         |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 한국 | <ul> <li>대기업중심, 메모리 편중,</li> <li>시스템반도체/설계전문가 부족</li> <li>중견 팹리스육성 미흡</li> </ul>                                                        | <ul> <li>차세대소자 R&amp;D 투자 시작 (연<br/>180억/년-산업부, 미래부,<br/>기반역량미흡)</li> <li>지능형반도체등 시스템 반도체<br/>개발 지원(800억/년 목표,<br/>사업화 역량미흡)</li> </ul>                                                                                                              | 메모리분야<br>선두유지(인텔등<br>강력한 경쟁기업<br>출현으로<br>위험증가)     시스템반도체<br>기술수준 매우<br>미흡   |

| 미국 | <ul> <li>팹리스 선도, 광범위한 전문인력 보유, 제조업 기반 약화추세, 학계연구 축소 추세</li> <li>최근 중국 반도체 산업 육성 견제 필요성 인지</li> </ul>                                    | <ul> <li>정부, 민간 투자축소로 학계연구 대폭 축소</li> <li>차세대소자 투자 시작 (E2CDA, JUMP,650억/년)</li> <li>정부주도 혁신전략 수립 의지 표명 (구체적 투자계획 미발표, SEMATECH 규모 R&amp;D 추진가능 - 1500억/년, 이 사업은 미정, JUMP등으로 1차 투자 시작)</li> <li>백안관 TF 구성을 통한 정부/기업/학계를 통한 반도체산업 주도권 유지 의지</li> </ul> | 인텔 - 메모리<br>진출     퀄컴 - 팹리스모델<br>변경, 자체 칩생산     (차량용 반도체<br>선두 기업인<br>NXP합병) |

| 중국 | <ul> <li>해외기업 유치,<br/>기술도입 추친,<br/>팹리스 활성화<br/>성공, ROI에<br/>무관한 해외<br/>반도체 기업<br/>M&amp;A 전략</li> <li>(ex. 스펙트럼<br/>17억불 인수)</li> </ul> | <ul> <li>향후 10년간 180조 (1조위안) 규모 반도체 굴기지원 (반도체수입 50% 절감 목표): 신성장산업육성 "제조 2025"정책 중하나 (중국 경제참고보2015.9.30.)</li> <li>- 2020년까지 중국 반도체 산업연평균 성장률 20% 이상 목표발표 (2014.06)</li> <li>20조 (1200억위안) 규모의 "반도체 산업 투자기금"설립 (2014.09)</li> </ul>                   | • 막대한 투자를 기반으로 기술수준이 모든 분야에서 급격히 향상되고 있음. 일부 반도체 후방 산업은 국내 산업 대비 경쟁력 우위      |

| 유럽 | 일부 반도체 기업 명맥유지, 산업영향력 미흡                                                                                                                | • ICT31을 비롯, 조단위 투자<br>R&D 진행, 나노기술과 반도체<br>연계 취약                                                                                                                                                                                                    | 기초기술은<br>우수하나,<br>산업연계 매우<br>취약                                              |

| 대만 | • 파운드리(위탁 제조) 중심                                                                                                                        | • 정부의 체계적 지원 미흡                                                                                                                                                                                                                                      | 퀄컴의 자체<br>칩생산으로<br>파운드리 수익률<br>악화                                            |

| 일본 | • 제조업 기반<br>약화                                                                                                                          | <ul><li>기초연구 정부지원 대폭 축소<br/>(신기술개발 실패)</li><li>단기, 응용연구 지원<br/>(전력반도체 중심)</li></ul>                                                                                                                                                                  | • 일부 신소자 기술<br>세계 선도 (STT<br>MRAM등)                                          |

- 핵심 경쟁국가별 차세대 반도체 기술 개발 동향 가. 한국

- 세계 반도체 시장의 20%를 점유. 메모리시장을 과점하고 있으나, 80%에 해당하는 시스템 반도체 시장에서는 경쟁력이 없음

- 이 문제를 해결하기위해 다양한 노력을 했으나, 후발 주자로서의 한계 (설계 IP 부족, 파운드리 기술격차 추격실패)를 극복하지 못해, 시장점유율이 답보상태임

- 특히 대기업 중심의 산업구조로 파운드리 및 팹리스 산업육성 정책의 효과가 미흡 한 상태에서, 대기업의 폐쇄적 연구구조로 학,연의 연구생태계 위축

- 학연지워을 위한 나노팹 투자도 실질적인 연구력 향상으로 이어지지 못함

- 차세대 반도체관련 투자 전략

- 2013년 미래소자원천기술개발사업, 2015년 지능형반도체 사업, 선행공정플랫폼개 발사업, 2016년 나노소재원천기술개발사업등을 통해, 미래반도체기술을 개발하기 위한 선행투자진행중

- 반도체 연구특성상 소재/공정/소자/집적/설계/시스템 의 통합연구체계가 없으면 개별 프로그램단위의 사업으로 효과가 제한적임

- 향후 기존 반도체 기술과 차원이 다른 신소자기반의 설계 IP를 조기에 확보하고, 이를 활용한 팹리스, 파운드리 산업을 육성하지 못한다면, 반도체분야에서 현 수준의 산업 주도권을 유지하는 것은 매우 어려울 것으로 생각됨

### 나. 미국

- 최근까지 연방정부 또는 주정부 주도 프로그램들의 축소, 폐쇄 추세 유지 SEMATECH 폐쇄, CNSE 축소, NRI 종료등

- 인텔 등 민간기업중심으로 연방정부주도의 산업구조 개편전략 추진중

- Intel, Grobal Foundries, Qualcomm, Freescale, AMAT 등이 적극 참여 (DARP A도 참여한다고 함)

- 2018년 Starnet, NRI 프로그램 재개 (약 650억/년 규모): 별첨자료의 E2CDA, J UMP 프로그램 call for proposal 참조

- 차세대 기술 initiative에 대한 강력한 정부투자 의지 제시

- 미국은 고급 연구인력을 다수 확보하고 있어, 새로운 소자, 새로운 아키텍쳐 기반의 차세대 CPU, AP등의 고급기술 선점에 주력할 것으로 예상됨

#### 다. 중국

- 정부 주도로 반도체 굴기 위해 기업, 대학, 연구소 등 산학연 연맹 결성

- 반도체 기초 연구부터 소재, 장비, 칩 제조의 생태계 구축

- 칭화유니, XMC, SMIC, 화웨이, ZTE 등의 반도체 기업 참여

- 중국 정부는 반도체 분야 중점 육성을 위해 2020년까지 총 53조 7075억원 투자 계획 (2010년부터 반도체를 7대 전략적 신흥 산업으로 육성)

- 2014년 정부 주도로 220억달러 규모의 반도체 퍼드 조성

- 메모리 반도체 국산화 위해 대규모 투자 진행 (칭화유니 13조 6000억, XMC 27 조 2000억)

- 중국은 제조기술 중심으로 기존 반도체 시장, 특히 메모리시장을 확보하면서, 팹리스 산업의 비중을 확대해갈 것으로 생각됨

#### ■ 소자워천 기술 개발 동향

- 초저전압 소자 및 회로 기술: 새로운 반송자 주입 방식 소자

- 2011년 IEDM 학회에서 G. Dewey가 최초로 sub-60-mV/dec를 상온에서 시연한 화합물 반도체 기반 tunnel FET을 발표

- 2012년 IEEE EDL에 L. Lattanzio가 electron-hole bilayer를 이용한 2D 구조의 tunnel FET을 발표

- 2013년 J. Wan이 IEEE EDL에 tunnel FET과 BJT의 동작을 결합하여 구동전류의 향상을 얻은 결과를 발표

- 초저전압 소자 및 회로 기술: Negative capacitance FET

- 2015년 Nature Materials에 ferroelectric negative capacitance 측정결과가 보고됨

- 다양한 ferroeletric소재를 이용하여 구성된 소자 연구결과가 보고되고 있으나, 아직 실용적인 수준의 결과가 보고된바 없음

- 2016년 APL에 J. H. Park이 single-grain PZT ferroelectric NCFET을 구현하여 우 수한 fatigue (> 10<sup>8</sup> cycle) 특성을 보고함.

### ○ M3D 기술

- 수년전 Samsung 및 SK-Hynix에서 초기 M3D에 대한 연구를 진행하였으나 (S3 Technology, Single Crystal Si Layer Stacking Technology) 당시 연구 장비 및 수준이 현재의 해외 leading 연구에 미치지 못하였고 그 당시 대비 많은 관련 장비 및 기술이 성숙되었고 미세화 한계 극복의 방법으로 M3D에 연구 필요성이 증대됨

- 국내 M3D에 대한 연구프로그램은 전무하며, 2015년 산업핵심 소재부품 반도체 산업프로그램에 관련 연구 시작이 예상되나 연구내용은 탐색 수준이 그침. (4억/년, 미래반도체소자프로그램)

- 다수의 국가에서 많은 연구가 진행되고 있으며 특히 Qualcomm은 기술 상용화에 대한 계획을 가지고 있음

### ○ 자기 재구성 로직 소자기술

- 자기재구성소자연구에 필요한 단위소자로 기계적스위치, atomic switch, 저항변화스 위치등 다양한 기술이 연구되고 있으며, 이를 이용한 단위회로에 대한 연구도 어느 정도 수행된 상황이어서, 지적재산권 확보가 쉽지않은 분야임

- 다만 자기재구성 소자를 BEOL구조에 삽입하여, FEOL CMOS회로와 융합하는 개념의 연구는 아직 초기 단계이므로, 이 부분에서 원천기술 창출가능성이 높음

- Relay소자는 UC Berkeley, Stanford, NIMS, 서강대, KAIST등에서 연구되고 있음

- Atomic switch는 LETI, Univ., 포항공대, 서울대등에서 연구되고 있음

- FPGA기반 자기재구성 시스템은 XILINX, ACTEL, Cypress등에서 연구되고 있음

### ○ 다치로직소자기술

- 다치로직을 상온에서 단위소자로 구현할 수 있는 기술은 아직 보고된 바 없으나, 다치로직 아키텍쳐에 대해서는 연구가 잘 되어 있어서, 단위소자를 개발하기위한 연구가 중심이 되는 분야임. 대부분의 경우 여러개의 소자 또는 복합소자를 이용하 여 삼진로진 구현

- 공명터널링트랜지스터 및 공명터널링다이오드 이용: 일본 NTT LSI 연구소, KAIST

- 단전자 트랜지스터 이용: Hokkaido 대, 충북대(2006)

- 양자점 트랜지스터: Connecticut 대(2009), Intel (2014)

- 그래핀/CNT: IMT Bucharest, 광주과학기술원 (2015, 2016)

- CMOS기반: 울산과학기술원

### ○ 로직-인-메모리 소자기술

- 2013년 Tohuku 대학에서 강유전체 Capacitor와 로직 소자를 집적된 로직-인-메모리 소자를 HSPICE 시뮬레이션을 통해서, 비 휘발성 특성의 강유전체 특성이 반영되어 정적 파워 소모를 혁신적으로 줄였으며, 다양한 논리 회로 (AND, OR, MUX-AND, MUX-OR,, )의 기능을 확인함.

- 2013-15년 독일 Fraunhofer 논문에서 실리콘 도핑된 하프니아를 이용하여 트랜지스터 기반 메모리 윈도우와 전하 유지능력에 대해서 보고함. 전하유지 성능이 우수하여, Endurance만 확보 (10<sup>15</sup>) 된다면, DRAM 향 소자에 적합한 것으로 예상됨.

- 일본의 ImPACT라는 대형 프로그램(40억엔)을 통해 무 충전 장기 사용가능한 에 코IT 용 스핀 로직-인-메모리 연구 개발 중임. 일본 도후쿠 대학중심의 IRST 프로그램을 통해서 MTJ를 이용한 비휘발성 CMOS 회로 (spin VLSI) 스핀 로직과 스핀 메모리 각자의 단위공정 기술에 연구 역량 집중됨. 세계적으로 스핀 기반 로직-인-메모리 아키텍쳐만 제시된 초기 사업단계임.

#### ○ 광배선소자기술

- 광배선 기술은 미국의 Intel이 선도하며 데이터 센터의 광트랜시버 용도로 제품 적용이 시작될 것으로 보이며, 유럽의 ST Microelectronics 또한 데이터 센터 용도로 제품 개발을 진행하고 있음. 연구기관으로서는 유럽의 IMEC이 연구를 주도하며 MPW foundry를 지원하고 있으며, 최근 미국에서는 5년간 \$600M의 거대 연구 프로젝트로 AIM photonics 시작되어 IMEC처럼 MPW foundry 지원을 준비하고 있음.

- 국내에서는 삼성전자가 Intel에 버금가는 수준으로 기술개발이 이루어지고 있으며, ETRI, KAIST, 연세대, 인하대 등에서 관련된 기초연구가 수행되고 있음.

#### ■ 뉴로모픽 소자기술

- 현재 뉴로모픽 소자 및 회로 연구는 IC 총 면적은 줄이고 메모리 셀 개수는 늘리는 고집적화에 초점이 맞춰져 있음. 따라서 전 세계적으로 다양한 고집적 신경망모방 회로 및 하드웨어 구조가 제안되고 있음.

- DARPA는 SyNAPSE 프로젝트를 통해 포유류의 뇌를 모방한 전자두뇌시스템 개방을 진행 중임. IBM은 SyNAPSE의 후속으로 SRAM 어레이를 시냅스 모방 소자로 활용한 트루노스(TrueNorth)라는 칩을 개발했으며 이 외에도 해외 많은 대학과 연구소들은 멤리스터 기반의 뉴로모픽 프로세서 연구에 집중하고 있음.

- 국내의 경우, 대학 및 연구소 중심으로 딥 러닝 및 인지 컴퓨팅 분야에 대한 연구가 진행되고 있음. 하지만 주로 소프트웨어적인 구현에 초점되어 있음. 하드웨어적인 뉴로모픽 프로세서 연구는 몇몇 대학을 중심으로 진행되고 있으나 이는 세계적인 추세인 멤리스터 및 SRAM을 이용한 뉴로모픽 시스템을 뒤따라 모방하는 수준에 그쳐 있음.

### 1.5. 국가 R&D 역량

■ 반도체 분야 국가 R&D 투자 현황

그림 9. 국내 차세대 시스템 반도체 연구 투자 현황

- (미래 반도체 핵심기술 개발) 정부와 기업이 투자자로, 대학·연구소는 연구개발자로 참여하는 새로운 형태의 R&D 프로그램(美 SRC모델)을 본격화함으로써 그간미흡했던 반도체 분야 원천기술개발 활성화 촉진

- 지난 4월 산업부-수요기업(삼성, SK하이닉스 등 6개社) 간 투자협력 MOU 체결 이후 금년 50억원(정부 25, 기업 25)이 투자된 바, 향후 투자금액을 지속 확대하 고 관련 부처와의 공동사업을 추진함으로써 미래 반도체 기술연구의 핵심 프로그램 으로 확대·발전시킬 계획

- 사업 예산 : '13년(50억원) → '14년(80억원) → '15~'17년(100억원 이상)

- 주요 연구분야 : 3-5족 채널 소자, Tunnel FET(터널펫), Optical interconnection 등

- 반도체 산업 재도약 전략 발표 (산업통상자원부, 2013년 10월 23일)

- (한국형 모바일 CPU코어 개발) 모바일用 반도체 생산이 급증하면서 칩설계의 기본이 되는 CPU코어 로열티 비용이 급증하고 있어 중소 팹리스기업 등의 비용부담이 나날이 가중되는 현실을 감안

- 13년에는 "저전력 프로세서 설계 기술개발(4년간 60억원)"을 시범적으로 추진하고, 향후 CPU코어 국산화 로드맵 도출(`14년) 및 관련 기술개발·상용화 등으로 지속 확대

- (450mm 장비개발) 조만간 현행 300mm웨이퍼를 대체할 것으로 전망되는 450mm웨이퍼용 대구경 장비 개발 프로그램(G450C\*)에 국내 장비업체를 참여시 킴으로써 기술의 선제적 확보 및 차세대 장비시장 선점 유도

- Intel, TSMC, IBM 등 5개 기업 중심으로 추진중인 450mm전용 장비 선행개발 국제공동 프로그램

- 대상분야 : 식각, 증착, 열처리, 세정 등 핵심 前공정장비 분야

- (수입의존형 SoC 국산화) 수입 규모가 크고 국내 기술개발 가능성이 높은 주요 SoC의 국산화율 제고를 위해 팹리스-수요기업 간 공동개발과제 (가칭'K-chip' 프로젝트) 추진

- 14년 이후 매년 3~5개 품목에 대한 연구개발 지속 추진(`14년 115억원)

#### ■ 국내 초절전 [CT분야 인력 현황

- 국내 대학원 학위취득자 현황

- 최근 3년간 국내 공학/자연계열 대학원 학위취득자의 총합은 석사 60,590명, 박사 16,551명으로 연평균 석사 20000여명, 박사 5500여명의 고급 인력이 꾸준히 배출되고 있음

- 이중 반도체 관련 전공분야 학위 취득자는 석사 8,367명, 박사 2,308명으로 각각 국내 공학/자연계열 대학원 학위취득자 전체의 19.5%, 23.0%에 해당함

- 현재의 인력공급 상황이 지속될 경우 9대 유망산업 분야에서 2013년부터 2020년까지 매년 1만여명의 핵심인재가 부족할 것으로 예상됨

- 특히 매년 25%이상의 시장성장이 예상되는 ICT 및 신소재나노 분야에서 매년 약 2500여명, 2020년까지 약 17000여명 가량의 전문 핵심인재 부족이 예상됨

- 기반 기술인 ICT 및 신소재 나노 분야에서의 인재부족이 장기화되면 향후 기술개발에 악영향을 미쳐 미래의 기술경쟁력 격차가 크게 확대될 우려가 있음

- 현 핵심인재 육성체계로는 미래 유망산업 분야에 필요한 기초과학 및 범용공학의 수요를 충당하기에 역부족임

#### ■ 초절전 ICT R&D 역량

- 공정/집적 분야 역량

- 기존의 Metal gate/High-k/high mobility channel 관련된 비메모리 공정 및 집적에 대한 보고가 지속적으로 이루어지고 있으며, 이와 관련하여 2D material등을 응용하는 공정들에 대한 보고는 낮은 수준에서 지속되고 있음.

- 메모리 소자 집적 공정에 관련하여서는 3차원 집적에 대한 보고가 지속적으로 이루어지고 있으며, 이를 위한 신물질 기반 신소자 집적 공정 적용에 관한 보고도 증

가하는 추세로 나타나고 있음.

#### ○ 소자분야 역량

- 2011년부터 2015년까지 IEDM에 발표된 국내 기관 발표 논문들을 살펴보면, 메모리 분야 논문이 매년 가장 큰 비중을 차지하고 있으며 특히 ReRAM, PCRAM과 같은 차세대 메모리에 대한 성능 개선 연구가 주를 이루고 있다.

- 그 외에도 화합물 반도체 소자, FinFET 신뢰성, TFT 소자, solarcell, 2D Material 연구, Neural/neuromorphic system에 대한 연구가 일부 발표되고 있음

- 차세대 신소자기술은 미국,유럽, 일본등에서 연구되는 있는 수준에는 크게 못미치며, 국내 연구그룹의 숫자도 10개 그룹 이내임.

#### ○ 설계/시스템 분야 역량

- 2011년부터 VLSI Symposium에 발표된 국내 기관 발표 논문들을 살펴보면, 저전 력화, 소형화, 고속데이터 전송에 필요한 핵심 기술에 대한 연구가 주를 이루고 있다.

- 선진국대비 국내 설계전문인력은 크게 부족한 상황이며, 특히 시스템설계, 아키텍 쳐연구분야의 전문가가 절대적으로 부족한 실정임

### ■ 타 사업과의 차별성

- 본 사업은 타부처(산업통상자원부)에서 현 시장 지배력 강화, 국산화 목적으로 기업 중심으로 추진하고 있는 대규모 산업화 관점의 반도체 기술 사업들과 달리, 차세대 반도체 산업의 글로벌 기술경쟁력을 확보하기 위해 공공부문 연구주체의 창의적인 혁신역량을 집약하여 최단기간 내 상용화 수준의 기술을 개발하고자 하는 사업임

- 산업부에서 추진중인 미래소자원천기술개발사업은 상용화시점기준 5년이내의 단기연구를 대상으로 하고, 본 사업은 상용화까지 5-15년정도가 소요되는 중장기 기술을 대상으로 함

- 미래부에서 추진중인 나노·소재원천기술 개발사업 중 반도체 분야 과제들은 본 사업에서 제안하고 있는 top down기술 중 일부를 선행개발하는 시범사업의 성격을 가지고 있음.

- 소자원천기술 개발의 시급성을 고려하고, 소자개발과 시스템집적기술 개발과제 사이에 1-3 년정도의 선행개발기간을 두기위한 전략임

- 위 그림은 기본소자기술의 기술적 복잡도 (신규기술이용정도), 목표상용화시점을 기준으로 본 사업과 기존사업간의 차별성을 도식화한 것임. 이 차트에서 소자기술 상용화시점이 지난 지능형반도체 과제는 이미 상용화된 실리콘 CMOS기반의 소자기술을 이용하는 대신 소프트웨어를 고도화하여 응용시스템을 개발하고 있는 과제라는 것을 볼 수 있음.

| 구분  | 동 사업  | 미래소자원천 | 나노소재원천 | 지능형반도체사 |

|-----|-------|--------|--------|---------|

| 1 七 | S 1 H | 기술개발사업 | 기술사업   | 업       |

|      |                                                                  | (산업부)                            | (미래부)                            |                                |

|------|------------------------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|

| 총사업비 | 4,500                                                            | 500 (정부)                         | 250                              | 850                            |

| (억원) | 4,300                                                            | 500 (민간)                         | 230                              | (가변적임)                         |

| 기투자액 | 0                                                                | 300                              | 50                               | 45                             |

| 사업기간 | `18-`27<br>(5년+5년)                                               | `13-`21                          | 5년                               | '14-'19                        |

| 사업목적 | 미래반도체 소자,<br>단위공정, 집적공<br>정, 설계기술 및<br>시스템개발                     |                                  | 단위 신소자 개<br>발 및 집적공정,<br>아키텍쳐 연구 |                                |

| 세부내용 | 7대 원천소자기술<br>중심으로 집적설<br>계플랫폼 및 인프<br>라 구축을 통한<br>차세대 시스템 개<br>발 | 디곤 계열 줄실<br>의 단위 반도체<br>소자워처기숙 개 | 신조사 기술을<br>이용하 시스테               | SOC 소프트웨<br>어 및 CMOS기<br>반 센서등 |

| 차별성  | 중장기과제중심                                                          | 단기과제중심                           | 중장기과제중심                          | 신 소 자 기 술 을<br>사용하지 않음         |

### 1.6. 사업 추진전략

### [전략 I ] 소자/시스템 계층통합형 사업으로 소자원천기술의 상용화 기간 단축

- CAD 기반기술을 최대한 활용, 세상에 존재하지 않는 신소자기반 설계기술 개발 및 시스템 성능 검증

- 국내 나노인프라 기반 시설을 융합, 신소자기반 중규모 집적회로 제작 환경을 구축하여, 소자연구분야의 국제경쟁력 확보

- 중규모 집적이 가능한 상용화 연구를 통해 공정, 소재, 장비, 설계등 중소기업 기술이전 연계효과 극대화

### [전략 II ] 글로벌 오픈이노베이션 체계를 활용한 글로벌 기술리더쉽 확보

- 해외 유사 프로그램과의 적극적 공동연구를 통한 투자 효율 극대화

- 국내전문인력 부족분야에 해외전문가 그룹을 적극 활용

### [전략 III ] 글로벌 컨소시움 추진, 투자효율 극대화를 위한 단일 사업단 체계 구축

- 국제적으로 국내 미래반도체 연구를 대표하는 연구집단 형성

- 소재부터 시스템까지 개발과정을 통합한 사업단 체계로 개발효율 극대화

- 1단계사업 글로벌 관련 정부 프로그램 네트웍 구성, 2단계사업 글로벌 컨소시움 구성전략을 통해 2단계사업 민간 투자 유치

#### ■ 계층통합연구

- 전 세계적으로 미래 신소자 기술개발 동력이 취약하여 차세대 반도체 기술의 전망이 불투명한 상황에서 초저전력 미래반도체 분야에서 고위험도, 도전적 소자연구부터 시스템까지의 여러 계층의 연구를 통합하여 추진하고, 선도적 성과를 조기에 확보함으로써 글로벌 기술 리더쉽을 확보하는 것을 목적으로 하고 있음

- 미국 SRC, SEMATECH, 유럽 IMEC, LETI, 일본 AIST, 대만 ITRI와 같이 외국의 경우 반도체 분야를 대표하는 연구기관 또는 연구프로그램이 있음. 초저전력미래반도체 사업단은 국내 미래반도체연구를 대표하는 연구프로그램으로서의 역할을 수행

### ■ 1단계 사업기간동안 글로벌 리더쉽 확보후, 2단계 글로벌 컨소시움 추진

- 차세대 소자기술 투자리스크를 저감하고, 표준화를 유도하기위해서, EU, 미국, 중국, 일본등에서 초저전력 관련 대형 R&D 프로그램간 협력네트웍을 구성하고 협력함

- 2단계 사업 (2023-2027)은 1단계 사업중 준비된 기반을 활용하여, 글로벌 건소시움을 구성하고 총 투자의 약 25%정도에 해당하는 민간기업의 투자를 확보하는 것을 목표로 설정

### ■ 혁신적 계층통합형 신소자개발 전략 적용

- 신소자 개발과 소재, 단위공정, 집적공정, 설계기반, 시스템 아키텍쳐 설계 기술을 통합 개발함으로써 소자기술의 상용화가능성을 최단기간내에 검증

- CAD (computer aided design)기술의 발전을 최대한 활용, 통합개발의 효율을

극대화함

#### ■ 전후방 수요연계 극대화 전략

- 1단계에는 연구목표 설정의 창의성, 기술개발의 독립성을 확보하기위해 투자예산의 100%를 정부에서 부담하나, 운영위원회, 기술자문위원회를 통해 산업계의 의견을 충분히 반영하도록 함

- 2단계 사업의 전제조건으로 지적재산권 비용부담등 선투자를 확보함으로써, 소자연구와 공정, 장비, 설계툴등 전후방 중소기업 연계를 활성화하여, 기술표준화 효과를 극대화 함

### ■ 나노소자집적 인프라 활용 전략

- 대학, 출연연의 개별연구그룹에서 신소자기술에 대한 기본 개념 검증 완료

- 핵심 소자 기술 및 아키텍쳐 기술을 기반으로 단위 소자 및 array 수준의 집적공정을 국내 나노 인프라 시설을 활용하여 수행할 수 있는 수준으로 나노집적공정 플랫폼 인프라를 구축하고, 관련 집적 기술 개발을 진행함.

- 나노집적공정 플랫폼 기술 개발은 국내 인프라 시설들의 상호연계를 기본 전략으로 함.

그림 10. 7대 소자의 집적을 위한 나노집적 인프라 연계 전략

### 1.7. 사업 추진체계 및 운영방안

### ■ 사업 추진체계

### ■ 거버넌스 체계 구성 배경

- 사업의 목표를 효과적으로 달성하고 빠르게 변화하는 대외 동향에 능동적으로 대처하기 위해서는 개별형 과제로 추진하는 것 보다는 독립적인 연구조직을 통해 수행하는 것이 바람직함

- 초저전력 미래반도체 사업은 국내 관련 연구역량을 총결집하여 차세대 기술을 효율적으로 개발하고, 한국 주도의 글로벌 연구컨소시움 구성함으로써 미래 기술의 주도권을 선점하기 위한 하향식(Top-down)의 사업임

- 본 사업은 기술개발(2022년) 및 제품개발(2025년) 시기, 제품 사양(소모전력 1/1000 이하, 메모리 저장능력 및 정보처리 속도 100배 이상) 및 종류 등의 목표가 명확한 "목표지향적" 사업임

- 반도체는 기술의 속도가 매우 빠르게 변화하는 분야이므로 급격히 변화하는 국제 정책·기술·산업 동향의 흐름을 신속히 파악하여 적기에 Moving target 설정을 위한 R&D 기획이 필요함

- 장기·초대형 연구개발 사업을 효율적으로 운영·관리하기 위해서는 사업단장의 역량 이외에도 기획·관리 기능을 갖춘 하부조직이 필요함

- 본 사업은 10년간 총 4,500억원(연평균 450억원)이 투입되도록 설계되어 단일 목표를 가진 사업으로는 최상위 그룹에 속하는 장기 대형 국가연구개발 사업임

- 사업단장이 연간 450억원 규모의 수행과제를 직접 기획·관리하는 것은 사업단장에게 업무 부하가 집중되어 비효율을 야기할 수 있음

- 본 사업은 기술개발, 시제품 개발 및 제품 확보를 목표로 하고 있어 연구와 비즈니스를 겸할 수 있는 사업단 조직이 적합함

- 사업단 조직은 R&D에 초점이 맞추어져 있어 기초·원천기술의 개발이나 환경분야와 같은 공공적 성격이 강한 연구개발 사업에 적합함

### ■ 사업 추진절차

- 본 사업은 독립 법인 형태의 단일 사업단 체계로 구성하고, 1단계 연구(5년) 2단계 연구(5년)로 구성

- 1단계 사업목표(2018-2022): 핵심원천기술 도출 및 민간 기업 참여유치

- 2단계 사업목표(2023-2027): 핵심 사업화 목표 달성 초절전/고성능 나노소자기 술 적용 메모리, 로직 통합 반도체 소자 확보

### ○ 추진내용

- 5대 나노정보전자기술 분야의 단위소자기술 초반 확보

- 기술표준화 및 글로벌 오픈 이노베이션을 통한 IP확보

- 하향식(Top-down) 방식을 통해 국가 R&D전략 및 사회적 수요에 부합하는 초저전력 미래반도체 기술 개발

- 하향식의 단점을 보완하기 위해 단일 사업단을 구성하고, 단장/부단장이 단위과제를 일괄 관리

|          | 하향식 (Top-down)                                                                                         | 상향식 (Bottom-down)                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 추진<br>체계 | •국가전략에 입각한 우선순위<br>배정으로 전략적 재원 배분 가능                                                                   | •창의적 아이디어 및 합의에 의한<br>자발적 조직화 특징                                                                                             |

| 장점       | •신속하고 효율적인 시스템 구성<br>•정량적 업무평가 가능                                                                      | •창의성 및 자유도 높음<br>•변화의 흐름에 빠르게 적응 가능                                                                                          |

| 단점       | <ul> <li>잘못된 목표 설정 시 지불해야 하는<br/>대가가 큼</li> <li>전세계적으로 빠르게 변하는<br/>연구시류에 효과적으로 적응하기<br/>어려움</li> </ul> | <ul> <li>목표에 대한 이해 및 공유가 부족한<br/>경우, 비효율적 운영 가능성 높음</li> <li>책임소재의 불명확성으로 인해<br/>업무추진 및의사결정 과정에서<br/>비효율적일 가능성 높음</li> </ul> |

### ■ 과제선정평가

- ''초저전력 미래반도체 원천기술' 로드맵에 근거하여, Top down 방식의 과제이므로 기술목표달성에 적합한 과제 수행전략 및 과제 수행능력을 중심으로 평가

- 시장지배력 확보 가능성, 기술혁신 기여도, 세계적 수준의 연구결과 도출가능성 평가

- 연구팀의 수월성 및 개발하고자 하는 기술의 사회경제적 파급력, 학제간·이종기술 연구자간의 역할분담의 적절성, 향후 초저전력반도체 분야 원천 특허 및 기술의 확 보 가능성 등을 평가

- 서면 및 발표평가 시행: RFP 부합성, 연구 계획의 창의성 및 도전성, 연구 목표의 명확성 및 타당성, 원천 기술의 확보 및 사업화 가능성, 연구진의 우수성 및 선행

연구 경험

- 국제협력과제 평가의 기본 방향

- 국내 파트너와 협력연구의 가능성 및 필요성

- 해외거점연구팀은 해당 분야 요소기술 연구를 수행하고, 플랫폼 기술은 국내 연구 팀이 개발하며 전체 연구성과를 통합하도록 구성

- 예비계획서에서 국내 및 해외 연구팀의 우수성과 공동연구 네트워크 구축 정도를중 심으로 평가

- 본 사업계획서에서 국내-해외 연구팀 간 유기적 연계, 역할분담 및 단계별 목표 달성 등 연구계획 중심으로 평가

### ■ 연차 및 단계 평가

- 연차 및 단계 평가의 기본 방향

- 연구 초기(1-2년)의 연차 평가는 성과 위주의 정량적 성과와 도전성을 집중적으로 평 가하되, 중기 이후(3-5년)에는 연구개발된 성과의 원천성 및 특허 확보를 집중적으로 평가

- 1단계 평가 결과를 반영한 2단계 연구비의 조정 운영 시행

- 단계 평가는 1-4년 동안의 연차평가의 결과를 70% 반영하고, 1단계 완료 시점에 5년 연차 평가와 함께 시행

### ■ 과제선정 평가단 구성

- 신규선정과 수시 선정은 동일한 평가 시스템 적용 (1단계 평가)

- 사업단장 선정, 부단장선정 및 3개월간의 사업준비기간을 거친 후 본 사업 시작시 신규과제선정 진행.

- 준비기간동안 운영위원회, 기술자문위원회를 구성하고, 각 위원회 중심으로 신규과제 및 수신과제 선정

- 반기별, 연차별 평가를 통해 탈락과제, 보완과제에 대한 수시선정 진행

- 신규과제의 선정은 기술자문위원회 중심의 평가단에서 1차 평가후, 기술자문위원회에서 2차 서면 평가후 사업단 운영위원회에서 최종결정

- 잠재적 투자기업의 대표를 평가단에 포함시키고, 1인이상의 특허 전문가를 포함하여 특허가치에 대한 평가시행

### 1.8. 투자 계획

■ (사업기간) 10년 (1단계: 2018~2022년, 2단계: 2023~2027년)[시범사업 2년 (2016~2017년)]

■ (사업비 규모) 1단계 총 2,000억원, 2단계 2,500억원 (시범사업 320억 별도)

| 세부사업 | 사업내용       | 총사업비 | 국고   | 지방비 | 민자   |

|------|------------|------|------|-----|------|

|      | 소자원천기술개발   | 700  | 550  | _   | 150  |

|      | 공정원천인프라개발  | 300  | 150  | _   | 150  |

|      | 나노인프라개발    | 350  | 200  | _   | 150  |

|      | 집적기술개발     | 600  | 350  | _   | 250  |

| 기술개발 | 글로벌오픈이노베이션 | 375  | 175  | _   | 200  |

| 기물개물 | 설계인프라개발    | 375  | 250  | _   | 125  |

|      | 신소자기반 아키텍쳐 | 400  | 300  | _   | 100  |

|      | 초저전압 시스템   | 300  | 300  | _   | _    |

|      | 뉴로모픽 시스템   | 350  | 350  | _   | _    |

|      | mW급 프로세서   | 400  | 400  | _   | _    |

| 기반   | _          | _    | _    | 1   |      |

| 구축   |            |      |      |     |      |

| 기타   | 총괄 관리      | 350  | 225  | _   | 125  |

|      | 소계         | 4500 | 3250 |     | 1250 |

### ■ 사업비 산출근거 (1단계 예시)

단위소자 개발과제 10억 \* 5년 \* 7건 = 350억 단위공정 개발과제 2억 \* 5년 \* 10건 = 100억 집적공정 개발과제 10억 \* 5년 \* 4건 = 200억 나노인프라보완투자 3억 \* 5년 \* 10대 = 150억 국제협력 2.5억 \* 5년 \* 10건 = 125억 설계인프라구축 15억 \* 5년 \* 3건 = 225억 신소자기반아키텍쳐10억 \* 5년 \* 5건 = 250억 초저전압시스템 10억 \* 5년 \* 3건 = 150억 뉴로모픽시스템 10억 \* 5년 \* 3건 = 150억 mW급 프로세서 10억 \* 5년 \* 3건 = 150억 총괄관리 30억 \* 5년 = 150억 소 계 = 2,000억

|         | '18 | '19 | '20 | '21 | '22 | '23 | '24 | '25 | '26 | '27 | 합계  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 총괄 관리사업 | 10  | 10  | 10  | 10  | 10  | 20  | 20  | 20  | 20  | 20  | 150 |

|        | 총괄             | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 100   |

|--------|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 夢。     | 소자원천<br>기술개발   | 70  | 70  | 70  | 70  | 70  | 70  | 70  | 70  | 70  | 70  | 700   |

| 랫<br>폼 | 공정원천<br>인프라개발  | 20  | 20  | 20  | 20  | 20  | 40  | 40  | 40  | 40  | 40  | 300   |

| 기<br>술 | 나노인프라<br>개발    | 30  | 30  | 30  | 30  | 30  | 40  | 40  | 40  | 40  | 40  | 350   |

| 개<br>발 | 집적기술개<br>발     | 40  | 40  | 40  | 40  | 40  | 80  | 80  | 80  | 80  | 80  | 600   |

| 包      | 글로벌오픈<br>이노베이션 | 25  | 25  | 25  | 25  | 25  | 50  | 50  | 50  | 50  | 50  | 375   |

| 2)     | 총괄             | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 100   |

| 시스     | 설계인프라<br>구축    | 45  | 45  | 45  | 45  | 45  | 30  | 30  | 30  | 30  | 30  | 375   |

| 템<br>집 | 신소자기반<br>아키텍쳐  | 50  | 50  | 50  | 50  | 50  | 30  | 30  | 30  | 30  | 30  | 400   |

| 적<br>기 | 초저전압<br>시스템    | 30  | 30  | 30  | 30  | 30  | 30  | 30  | 30  | 30  | 30  | 300   |

| 술<br>개 | 뉴로모픽<br>시스템    | 30  | 30  | 30  | 30  | 30  | 40  | 40  | 40  | 40  | 40  | 350   |

| 발      | mW 급<br>프로세서   | 30  | 30  | 30  | 30  | 30  | 50  | 50  | 50  | 50  | 50  | 400   |

|        | 합계             | 400 | 400 | 400 | 400 | 400 | 500 | 500 | 500 | 500 | 500 | 4,500 |

|        | 정부투자           | 400 | 400 | 400 | 400 | 400 | 250 | 250 | 250 | 250 | 250 | 3,250 |

|        | 민간투자           | •   | •   | •   | •   | •   | 250 | 250 | 250 | 250 | 250 | 1,250 |

### ■ 인력 투입계획

|        | '18       | '19  | '20  | '21  | '22  | '23  | '24  | '25  | '26  | '27  | 합계     |

|--------|-----------|------|------|------|------|------|------|------|------|------|--------|

| 박사급(명) | 200       | 200  | 200  | 200  | 200  | 200  | 200  | 200  | 200  | 200  | 2,000  |

| 석사급(명) | 400       | 400  | 400  | 400  | 400  | 400  | 400  | 400  | 400  | 400  | 4,000  |

| 학사급(명) | 400       | 400  | 400  | 400  | 400  | 400  | 400  | 400  | 400  | 400  | 4,000  |

| 합계(명)  | 1,00<br>0 | 1,00 | 1,00 | 1,00 | 1,00 | 1,00 | 1,00 | 1,00 | 1,00 | 1,00 | 10,000 |

### ■ 소요인력 산출근거

- 인건비 : 400억 × 30% = 120 억원/년 내외

- 책임자급 200명 상정

- $\bigcirc$  박사후 연구원 : 책임자급 연구실별로 1명 imes 참여율 50%

- \* 박사후 연구원 1명 × 400만원(월급여) × 12개월 = 58억원/년

- $\bigcirc$  박사과정 (책임급 수 imes 2명/년), 석사과정 (책임자 수 imes 2명/년) imes 참여율 30%

- \* 박사과정 1명 × 250만원 × 12개월 = 36억원/년

\* 석사과정 1명 × 180만원 × 12개월 = 26억원/년

### 1.9. 타당성 분석

#### ■ 정책적 타당성 분석

#### ○ 사업추진의 시의성

- 전력문제(생산 및 사용) 해결 관련 기술이 최근의 모든 분야의 산업에 필수적으로 요구되어지고 있으며 특히 반도체 산업 분야에서도 전력 사용 문제 해결을 위한 새로운 패러다임이 요구되고 이를 통해 신 시장을 창출할 수 있는 도전적이고 창의적인 연구가 필요함.

- 지금까지 민간에 의존해온 반도체 분야의 연구는 단기적 결과에 치우친 연구에 국하되었고 중장기 연구에 대한 연구가 미흡한 상태로 정부의 지원이 필요함.

- 미, EU는 미국주도의 기술개발체계가 취약해진 시점에서, 반도체 분야의 기술 주 도권을 확보하기위해 정부차원에서 지원을 하고 있으며, 후발 주자인 중국은 현재 의 반도체 산업에 진입을 하기 위해 정부차원에서 많은 지원을 하고 있는 상황임.

- 이러한 상황을 극복하기 위해 새로운 산업을 창출할수 있는 초저전력 미래반도체 분야에 대한 정부 지원으로 기존의 반도체 강자와 신흥 국가를 따돌리고 주도권을 선점할 수 있도록 정부 차원을 지원이 절실히 필요함.

#### ○ 정부지원의 필요성

- High risk, high return 형 차세대 기술은 세계적으로 정부주도의 연구프로그램에 의해 선행개발되고 있음. 미국, EU등 경쟁국가들은 2016년부터 본격적인 정부주도형 투자를 시작함

| <반 | 도체 | 산업 | は보유 <sup>.</sup> | 국가들의 | 리 주요 | 반도체 | 연구프로그 | .램 - | 투자규모> |

|----|----|----|------------------|------|------|-----|-------|------|-------|

|----|----|----|------------------|------|------|-----|-------|------|-------|

|    |           | 총 연구 금액         |                |        |

|----|-----------|-----------------|----------------|--------|

| 국가 | 5년이내      | 5 - 15년 이<br>내  | 15 년 이후        | (억)    |

| 미국 | 843 (5%)  | 13,916<br>(75%) | 3,796<br>(20%) | 18,555 |

| EU | 614 (2%)  | 30,497<br>(85%) | 5,022<br>(13%) | 36,133 |

| 일본 | 656 (4%)  | 12,818<br>(88%) | 1,058 (8%)     | 14,532 |

| 한국 | 205 (20%) | 380 (38%)       | 427 (42%)      | 1,012  |

- 본 사업은 특정제품 기술개발이 아니라 공정, 소재, 장비, 설계기술등 반도체 제조 산업의 전후방산업 파급효과가 매우 큰 사업이기 때문에, 민간기업이 전체 사업을 초기부터 기획하고, 관리할 수 없는 구조여서 정부투자가 필수적임

- 기술표준화방향에 따라 신기술채택여부가 결정되기 때문에 민간기업이 본격적인 장기 선행투자를 진행하기 어려움

- 2020년대 중후반 시장이 열릴 것으로 예측되는 신개념 나노-반도체 융합기술은 경쟁국에서도 아직 기술적 우위를 확보하지 못한 상태여서 정부주도의 기반기술 투 자를 통해, 반도체 산업전반의 기술경쟁력을 확보할 필요가 있음

### ○ 국가 중장기 R&D 계획과의 부합성

- 과학기술기본계획과의 부합성

- 국가 전략 기술 수준 및 예산 증감률의 예를 보면 (아래 표), 경제 지속 성장 견인의 ICT융합 신산업 창출, 미래 성장 동력 확충은 선진국 대비 기술적 성숙도가 상대적으로 열약하여 기술 수준 향상을 위한 예산 배정 금액이 타 분야 보다 큰 것으로 판단하건대 ICT 융합 신산업 창출과 미래성장 동력 확충의 목표를 삼고본 사업의 중요가 현재 국가 과학기술기본계획의 방향과 부합한다고 판단됨.

- 기초연구진흥 종합계획과의 부합성

- 본 사업의 목표는 현재의 나노전자소자 분야 시장의 확대 뿐만 아니라 새로운 신산업 창출을 위해 창의·도전적인 재료, 공정, 설계, 장비 등 많은 분야의 기초 연구를 포함하여 새로운 반도체 및 나노 전자 분야의 신 생태계를 구축하고 이를 활용·확산 하는데 목표가 있기에 과제의 성격과 목표는 현재 정부의 기초연구진흥종합계획의 정책과제와 부합함.

- 국가융합발전기본계획과의 부합성

- 본 사업은 소재, 공정, 설계, 장비 등 많은 분야의 병렬적 융합적 개발의 성격을 가지고 있기에 다양한 분야의 융합적 신산업 창출이 가능함. 특히, 경제 성장 7대 분야의 중 차세대 반도체, 스마트 자동차, 차세대 소재에 직접적인 관련이 있으며 타 분야의 시스템을 구축하는데 있어 본 사업의 연구 결과가 기본 platform으로 제공될 수 있음.

- 신성장동력 종합추진계획과의 부합성

- 본 사업은 새로운 시장 창출 및 선점을 위한 소재, 공정, 설계, 장비 등의 융합 과제로 신성장동력 종합추진계획의 주력 연구 분야와 잘 부합함.

### ○ 기존사업과의 차별성 및 연계성

| -    |                                                          | - 기계 4 - 기이 - 기  | . li 2 -il 0l =l                   |                                                                                           |

|------|----------------------------------------------------------|------------------|------------------------------------|-------------------------------------------------------------------------------------------|

| 구분   | 동 사업                                                     | 미래소자원천<br>기술개발사업 | 나노소재원천<br>기술사업                     | 지능형반도체사업                                                                                  |

| , ,  | 0 / 1                                                    | (산업부)            | (미래부)                              | 7002                                                                                      |

| 총사업비 | 4.500                                                    | 500 (정부)         | 250                                | 850                                                                                       |

| (억원) | 4,500                                                    | 500 (민간)         | 230                                | (가변적임)                                                                                    |

| 기투자액 | 0                                                        | 300              | 50                                 | 45                                                                                        |

| 사업기간 | `18-`27                                                  | `13-`21          | 5년                                 | '14–'19                                                                                   |

|      | (5년+5년)                                                  |                  |                                    |                                                                                           |

| 사업목적 | 미래반도체 소자,<br>단위공정, 집적공정,<br>설계기술 및 시스템개<br>발             |                  | 단위 신소자 개발 및<br>집적공정, 아키텍쳐<br>연구    | ICT 융합 제품에서<br>SW와 SoC를 기반<br>으로 인지, 연산, 제<br>어, 통신 등의 지능<br>형 서비스 기능을<br>수행하는 핵심부품<br>개발 |

| 세부내용 | 7대 원천소자기술 중<br>심으로 집적설계플랫폼<br>및 인프라 구축을 통한<br>차세대 시스템 개발 |                  | 신소자 기술을 이용<br>한 시스템 전력소모<br>극단적 절감 | SOC 소프트웨어 및<br>CMOS기반 센서등                                                                 |

| 차별성  | 중장기과제중심                                                  | 단기과제중심           | 중장기과제중심                            | 신소자기술을 사용<br>하지 않음                                                                        |

- 본 사업은 타부처(지식경제부)에서 현 시장 지배력 강화, 국산화 목적으로 기업 중심으로 추진하고 있는 대규모 산업화 관점의 반도체 기술 사업들과 달리, 차세대 반도체 산업의 글로벌 기술경쟁력을 확보하기 위해 공공부문 연구주체의 창의적인 혁신역량을 집약하여 최단기간내 상용화 수준의 기술을 개발하는 사업임

- 산업부에서 추진중인 미래소자원천기술개발사업은 상용화시점기준 5년이내의 단기 연구를 대상으로 하고, 본 사업은 상용화까지 5-15년정도가 소요되는 중장기 기술 을 대상으로 함

- 미래부에서 추진중인 나노소재원천기술 개발사업중 반도체부분은 본사업에서 제안 하고 있는 7개원천소자기술을 선행개발하는 시범사업의 성격을 가지고 있음.

- 소자원천기술 개발의 시급성을 고려하고, 소자개발과 시스템집적기술 개발과제사 이에 1-3 년정도의 선행개발기간을 두기위한 전략임

- 본 사업에서는 소자기술에서 시스템설계기술까지의 개발기간을 최대한 단축함으로 써, 경쟁국대비 압도적인 기술 경쟁력을 확보하고, 선진국 대비 열세인 소자 및 설계기술 분야의 도약적 발전을 달성하고자 함

#### ■ 정책대안에 대한 타당성 분석

- [대안 1] 정부 투자를 하지 않는 대안

- 차세대 반도체 기술개발을 민간기업에 전담시키는 방법으로 기존 R&D 사업수준의 정부투자만 진행하는 방법

- 산업부 미래소자원천기술개발사업의 경우, 단중기 연구를 목표로 했으나, 민간기업의 단기연구선호로 인해 중장기연구 체계 구축이 어려운 상황임

- 선진국의 차세대 반도체 기술 장벽으로 인해, 기존 반도체 소자기업은 물론 장비, 설계 기업등 후방산업까지도 차세대 반도체 산업에서의 경쟁력상실

- 결과적으로 중국의 추격을 허용함으로써, 60조 규모의 반도체 소자 산업은 물론 전,후방산업의 동반 몰락이 예상됨.

### ○ [대안 2] 기존 R&D 사업 예산을 확대하는 대안

- 유사한 규모의 R&D예산을 교과부와 지경부의 기존 R&D 사업 또는 타 R&D 사업 에 투입하는 대안을 생각할 수 있음

- 산발적인 소자연구, 집중화되지 않은 나노인프라 공정, 통합설계기술연구 체계가 갖추어져있지 않는 상황에서는 대규모 투자의 효율성을 담보할 수 없음

- 특히, IMEC, LETI, CNSE 등 대규모 연구소와 안정화된 팹를 기반으로 집중적인 연구를 하고 있는 선진국과의 경쟁시 기술적 대표성을 확보할 수 없어서, 기술리더 쉽을 확보할 수 없음

- 선진국주도의 차세대 기술표준화를 따라갈 경우, 대안 1에서 제시한 것과 같이 기술장벽문제를 해결하기 어렵게 됨.

### ■ 비용효과 분석

○ 타당성 분석은 실물옵션(Real Option) 프레임워크에 의하여 수행됨. 실물옵션 프레임워크에서는 시장에서의 경쟁구조, 거시적 시장 환경 등 불확실성이 큰 기업의 경영 상황에서 기업의 투자에 관한 의사결정이 유연하게 이루어질 수밖에 없는

상황을 반영할 수 있음.

- 사업의 순 옵션가치는 약 187억 원임. 따라서 본 사업은 타당성이 있음. 향후 5년간 투입되는 사업비와 시범사업비와의 비율을 계산하면 약 8%의 수익률(옵션 프리미엄)을 예상.

- 사업의 순 옵션가치가 187억 원이므로 사업의 총 가치는 향후 5년간 투입되는 투자비의 현재가치인 2232억 원과 187억 원의 합, 즉 2419억 원이 됨. 이를 옵션 프리미엄으로 환산하면 187/2232, 약 8%의 수익률이 됨.

- 따라서 본 사업은 반드시 수행되어야 하는 가치 있는 사업임.

- 본 사업 옵션가치의 확률분포는 다음과 같음. 확률분포를 구하기 위하여 사업이 옵션가치를 총  $10^5$ 회 시뮬레이션을 하였음. 확률분포는 아래 그림과 표를 참고.

|          | Simulated Project Option Values (105 runs) |

|----------|--------------------------------------------|

| min      | -2,010.946                                 |

| max      | 25,664.25                                  |

| median   | -466.6303                                  |

| mean     | 187.8443                                   |

| std.dev  | 2040.581                                   |

| skewness | 2.602308                                   |

| kurtosis | 11.63693                                   |

|          |                                            |

- 참고로 중위수(median)는 음수로 약 -466.6억 원인데 이는 기술금융의 전형적인 패턴이기 때문에 우려할 필요가 없음. 벤처캐피털 등 기술금융이 가장 발달한 미국에서도 벤처의 성공확률은 25%이하임. 이는 중위수익률(median return)이음수임을 뜻함. 그러나 소수의 성공하는 사업에서 대단히 큰 수익을 창출하므로 전체 사업 포트폴리오의 수익률은 양수가 되는 것임.

- 본 사업에 대한 타당성 조사도 비슷한 패턴을 보임. 사업의 가치는 대단히 오른쪽으로 꼬리가 늘어지는 분포(right-skewed distribution) 형태임(Skewness = 2.6). 즉 이 사업은 여타의 기술벤처의 경우와 같이 잠재력이 크지만 실패하는 경우도 존재할 수 있음을 시사. 그러나 성공할 경우 대단히 큰 가치를 창출하게 될 것임.

- 타당성 분석을 위한 모형은 전력 절감에 관한 목표인 2021년까지 1/10, 2023년까지 1/100, 2027까지 1/1000가 달성된다는 가정 이외에 다른 모든 가정은 대단히 보수적으로 하였음.

- 목표 달성에 관한 위의 가정에 관하여 실패할 가능성도 명시적으로 타당성 모형에서 고려함. 본 사업이 기대했던 만큼의 가치를 창출하지 못할 경우 사업이 청산됨을 가정. 청산 후 가치도 없다고 대단히 보수적으로 가정함.

- 사업이 청산되더라도 논문 게재 등으로 발생하는 과학 성과와 탁월성 성과 등이 발생함. 이와 같은 학술적 성과를 청산비용에 감안할 경우 본 연구의 가치는 바로 그 성과의 현재 가치만큼 상승할 것임. (현재 본 연구진은 타당성 분석을 최대한으로 보수적으로 수행하기 위하여 이러한 학술적 성과는 일단 무시한 것임)

- 사업의 변동성이 커질수록 사업의 가치가 향상됨. 이는 현재 사업이 실물옵션 특성을 가지고 있으므로 당연. 따라서 공격적인 R&D를 장려할 필요가 있음.

# 1. 사업기획의 개요

## 1.1. 사업기획 추진 배경

■ ICT 기술이 발전함에 따라, 정보처리기기에서 소요되는 에너지의 총량이 기하급수적으로 증가될 것으로 전망

- 그림 1.은 미국 내 데이터센터에서 소모되는 전력비용의 증가추세를 보여줌.

- 2013년 데이터센터에 쓰이는 전력량은

원자력발전소 27기의 발전량에 해당함

- 2020년에는 개인용 IT기기에서의 사용량을 포함하면, 전체 에너지소모의 12-15%가 정보처리에 소모될 것으로 추정됨

그림 1.1. 데이터 센터의 전력소모 증가 추세

- 사물인터넷 도입에 의해 스마트 홈, 스마트그리드, 스마트 카, ubiquitous health care, 동영상 등에서 발생되는 정보처리 수요 폭증예상 (최대 백만 배)

- 이에 따른 데이터의 전송, 연산, 응용에 엄청난 에너지가 소모될 것으로 생각됨

- 현재의 컴퓨팅 체계로는 미래 에너지 수요를 감당할 수 없기 때문에, 소자, 아키텍쳐, 시스템 등 전 분야에 걸쳐 초절전 연산체계로의 패러다임 전환 필요

그림 1.2. 정보처리 소자 기술 변천과정

○ 1960년대 이후 반도체 기술의 발전을 주도했던 미세화 일변도의 기술 발전이 한계에 도달했다는 인식이 확산되고 있으며, 미래 정보처리기기의 과도한 에너지 소모에 의한 기술 정체를 막고 지속적인 발전을 위해 초저전력 미래반도체 기술 개발이 시급함

- 전세계적으로 미세화 기술의 한계를 극복하고, 초저전력 컴퓨팅기술을 구현할 수 있는 차세대 로직소자 및 연산기술 개발 경쟁이 본격화됨

- 획기적인 기술발전의 계기를 마련하지 못한 상태임

- 차세대 ICT 기기 (사물 인터넷, 스마트폰, 스마트 워치등 웨어러블 기기, 임플랜터블 기기, 초절전 고성능서버, 데이터센터 등)와 관련된 미래산업 경쟁력은 초저전력 미래반도체 기술이 결정하게 될 것임

- 인텔은 에너지 절감이 가능한 초절전 컴퓨터의 중요성을 인식하고, 이미 저전력 서버 시장의 95%를 선점한 상태임

- 저전력 반도체는 이미 전체 반도체 시장중 가장 큰 시장을 형성

|  |      | 201     | 4     | 201     | 5     | 201     | 6     | 201′    | 7     |

|--|------|---------|-------|---------|-------|---------|-------|---------|-------|

|  |      | 금액      | 비중    | 금액      | 비중    | 금액      | 비중    | 금액      | 비중    |

|  | 반도체  | 335,843 | 100.0 | 336,392 | 100.0 | 341,011 | 100.0 | 351,596 | 100.0 |

|  | 메모리  | 79,243  | 23.6  | 78,450  | 23.3  | 75,889  | 22.3  | 78,539  | 22.3  |

|  | 로직   | 91,633  | 27.3  | 90,212  | 26.8  | 91,753  | 26.9  | 93,785  | 26.7  |

|  | 아날로그 | 44,365  | 13.2  | 45,483  | 13.5  | 47,027  | 13.8  | 48,953  | 13.9  |

표 1.1. 세계 반도체 시장 규모 (자료: WSTS Forecast 2015 Fall, 단위: 백만달러)

- 초저전력 미래반도체 적용제품의 시장규모는 메모리와 로직반도체 시장의 30%정도로 추정가능 (2017년 기준 51,697M\$ (약 62조), 2025년 추정치 76,380M\$ (약 91조, 환율 1\$=1200원, CAGR 5%가정))

- 이 시장은 현재 한국의 반도체 산업의 규모를 2배이상 성장시킬수 있는 규모임

### ■ 선진국들의 발빠른 대응

○ IBM은 2025년 이후, 스케일링 기반 반도체 기술의 종말과 7nm노드 기술 이후 post CMOS 기술시대의 도래를 예측하고, 기존 반도체 기술의 패러다임을 획기적으로 전환하여 스케일링 없이도 낮은 전압에서 동작하는 초저전력, 고성능 연산 기술 개발을 선언함

○ 이를 기점으로 7nm 이후 스케일링의 한계를 극복하면서도, 차세대 ICT 기술 (스마트폰, 스마트 워치, 접는 노트북 등)에 적용 가능한 신개념 반도체 소자 원천기술 선점을 위한 본격 경쟁이 시작되었으며, 미국, 유럽, 일본 등에서는 차세대 scaling기반 기술은 물론 scaling을 필요로 하지 않는 새로운 형태의 정보처리기술을 개발하기 위해 대형 중장기 연구프로그램들을 다수 운영 중임

- 미국은 exa scale computing, sustainable computing technology란 개념으로 이 분야의 미래 원천기술에 대한 전반적인 연구가 활발히 진행되고 있음

- 정부 주도로 "Energy efficient computing for devices and architectures" 연구 프로그램을 2016년 하반기에 시작할 예정임 (초절전 반도체 신소자 기술과 아키텍쳐에 대한 연구 프로그램임)

- 유럽은 "ICT-31: nanoelectronics and microelectronics" 연구 프로그램을 2017년 1월에 시작할 예정임 (3차원 집적기술, 뉴로모픽 아키텍쳐 등 전력절감형 기술에 대한 연구 프로그램임)

- 그 외에도 TSV/M3M 등 소자 융합과 저전력을 위한 연구프로그램을 동시에 진행하고 있으며, 초저전력 시스템 구현을 위해 연산 아키텍쳐/회로/소자/소재에 대한 초대형 연구프로그램을 시작함.

- Qualcomm-LETI(프)-SMIC(중)-북경대 등 공동개발 진행

- 뉴로모픽의 경우 미, EU, 일본을 합쳐 2조원 정도가 투자되고 있음

#### ■ 대한민국 반도체기술의 현황

- 우리나라는 scaling 기반 공정기술에서의 우세를 바탕으로 시장을 확보해왔음

- 국내 주요 반도체 기업인 삼성과 SK 하이닉스는 미세화 공정 및 메모리 분야 이외의 미래기술에 대한 대응 전략이 미흡한 상황임

- 국내 산업계가 주로 이용해온 IBM alliance, SEMATECH\*, IMEC 등의 기술도입 선이 기술개발을 포기하거나, 매우 부진한 상황이어서, 독자기술개발의 필요성이 대두되고 있음

- \* SEMATECH: 삼성, Intel등 반도체기업들이 공동으로 자금을 출연, 기초연구를 수행하는 기관, 1983년 설립, 2015년 뉴욕주소재 CNSE에 합병

- 국내의 저전력 융합 소자, IoT 등 초연결 사회에 대비한 기반 연구는 매우 부족함

- 뉴로모픽 소자기술은 미래융합파이오니어 사업에서 일부 진행 중

| 국가  | 총 연구 금액   |              |             |        |

|-----|-----------|--------------|-------------|--------|

| 7/1 | 5년이내      | 5 - 15년 이내   | 15 년 이후     | (억)    |

| 미국  | 843 (5%)  | 13,916 (75%) | 3,796 (20%) | 18,555 |

| EU  | 614 (2%)  | 30,497 (85%) | 5,022 (13%) | 36,133 |

| 일본  | 656 (4%)  | 12,818 (88%) | 1,058 (8%)  | 14,532 |

| 한국  | 205 (20%) | 380 (38%)    | 427 (42%)   | 1,012  |

- 표 1.2. 세계 반도체 시장 규모 (자료: WSTS Forecast 2015 Fall, 단위: 백만달러)

- 위의 표에 정리된 바와 같이 현 정부의 미래소자 관련 R&D 투자는 중기과제대비 (38%) 대비 신기술분야 장기기술과제(42%)에 대한 비중이 높았는데, 이것은 전자소자 분야에서 대기업의 역할이 강조되면서, 학술적인 가치가 다소 적지만, 상용화가능성이 있는 소자기술에 대한 지원이 매우 제한적이었기 때문인 것으로 분석됨

- 이 추세가 지속된다면, 우리나라의 기반 산업인 반도체, 디스플레이 등 전자산업이 경쟁력을 상실하게 되고, 중국에 추월당하게 되는 것은 시간문제임

- 이 상황은 학술적 가치만을 중시한 편중된 국책연구 지원, 민간기업의 근시안적인 기술개발 전략과 기술수입에 의존하여, 국내 연구생태계를 파괴한 결과임

- 미국에서 반도체 제조가 퇴조하고, 연구지원에 축소되면서 R&D outsourcing이 확대되고 있으나, 반도체 분야에서의 국제공동연구 파트너로 한국이 아니라 대만, 중국이 선호되고 있음

- 중국은 전세계에 퍼져있는 화교인력을 기반으로 중국 내의 연구역량을 급속히 발전시켜나가고 있으며, 이러한 추세에 기인함.

## 1.2. 사업기획 추진 필요성

- 최근 팹리스의 등장으로 반도체 분야의 연구투자가 감소되고, 반도체 주생산국 간의 기술장벽이 높아지게 되면서 미래기술동향 예측이 더욱 어려워짐

- R&D 비용 절감방안이었던 컨소시움 형태의 공동연구방식 퇴조 (반도체 주생산국 간의 기술장벽강화, 2015년 SEMATECH 폐쇄 등)

- 미래 ICT 기반산업에서의 선도적 위치를 유지하고 경쟁에서 뒤처지지 않기 위해서는 차세대 혁신소자기술의 개념을 조기에 도출/검증하고, 이를 기반으로 광범위한 지적재산권 보호망을 선점한 후, 시장지배력을 확보하는 것을 최우선으로 하는 대책수립이 시급함

- 차세대 반도체 기술은 사물인터넷, 유비쿼터스화된 정보처리에 적합하도록 초저전력 연산 체계를 지원할 수 있는 기술이 필요하다는 점에는 개략적인 공감대가 형성되어 있으나, 구체적인 소자기술, 아키텍쳐에 대해서는 ITRS 등 기존 로드맵이나 기술 컨소시움들이 방향을 제대로 제시하지 못하고 있음

- 최근 논문발표 추세를 분석하면, 차세대 기술개발의 구심점이 유럽의 IMEC, LETI 등으로 일부 옮겨가고 있으나, 사물 인터넷 시대의 도래, 반도체 기술의 초저전력화에 따른 패러다임 전환 등 전면적인 기술환경 변화에 대응하기에는 매우미흡한 상태로 현재 반도체 산업의 미래기술을 선도하는 주체가 없는 상태임.

- 2020년대 후반경 도입될 신개념 정보소자 기술분야는 해외 선진 업체 주도에 의해 형성된 기존의 market에 국내 반도체 산업이 공정 최적화를 통해 진입했던 기존의 방식과 달리 아직 경쟁국가들이 기술적 우위를 확보하지 못한 초기 상태이므로, 집중적인 연구 개발을 통한 기술주도권 확보가 가능함

- 이를 위해 지금까지의 추격형 연구와는 달리, 패러다임 전환기 이후 반도체 및 나노전자기술 분야에서의 주도권을 선점하는 것을 목표로 하는 도전적인 연구개발 지원/추진 전략을 수립하는 것이 매우 시급함

#### ■ 정부지워의 필요성

- 초저전력 미래반도체기술은 IoT 시대의 ICT 기반기술로 반도체뿐 아니라 센서, 디스플레이등 다양한 분야에 파급효과가 매우 큼

- 선진 경쟁국들은 2016년부터 본격적인 정부주도형 투자를 시작

- 미국: 2015년 대통령 행정지시 (National Strategic Computing Initiative)이후,

Nanotechnology-Inspired Grand Challenge for Future Computing에 대한 수요조

사 실시(Oct.24, 2015), 2016년 NSF에서 Energy efficient computing 과제 추진

예정 (50억/년)

- 유럽: 2016년 ICT31 program을 통해, 초저전력 소자 및 시스템 과제공모 진행 중, 2017년 과제개시(65억/년)

- 국내 기존 반도체 기업들은 미세화 기술 경쟁의 가속화와 R&D 투자비용의 급증으로 인해 초저전력 소자에 대한 중장기연구 투자여력이 부족한 상황

- 초저전력, 고성능 나노소자 기술 개발을 위한 정부적 차원의 지원이 필요한 실정이며, 패러다임 전환형 기술의 선제적 도입여부에 따라 초연결사회의 기반산업인 반도체 산업의 미래도 크게 영향을 받게 될 것임

- 초저전력 미래반도체 기술 선점을 위해 아키텍쳐/회로/소자/소재 기술을 연결하는 계층통합형 중장기 연구프로그램이 필요함

- 현재의 반도체 기술은 향후 6년이내에 cost-performance cross over \* 가 일어날 것으로 예측됨

- \* cost-performance cross over: 차세대 기술 사용비용이 그에 따른 이익을 초과하는 현상

- 시스템 성능을 향상시키기 위해 필요한 비용을 억제하면서도 초저전력 시스템을 구성하기 위해 현재와는 전혀 새로운 반도체소자 및 활용 아키텍쳐 기술이 필요해짐

- 아키텍쳐/회로/소자/소재 반도체 전 분야 연구자들이 모여 초저전력 미래반도체 기술 개발이라는 목표를 조기 달성하기 위해 집중적인 연구가 필요

- 차세대 ICT 기반 부품, 소재, 장비등 광범위한 산업분야에서 선도기술 선점가능

#### ■ 대응 전략

- 국가 기반 산업인 반도체 산업의 기술적 우위를 지속하기 위해서는 단위과제 위주의 산발적인 R&D 투자로는 핵심 원천기술 확보 및 공정, 장비, 소자, 소재 간의 융합에 한계가 있음

- 반도체 산업의 기술 경쟁력 유지 및 강화를 위해 빠른 속도로 원천기술 (특허) 확보를 위한 기초·원천연구 프로그램 도입이 시급함

- 단일 연구조직의 필요성: 미국(SEMATECH), 유럽 (IMEC, LETI)과는 달리 국내에는 미래 반도체분야의 글로벌 연구 프로그램을 주도할 기관이 없는 상태임.

- 현 스케일링 기술의 한계를 뛰어넘는 새로운 패러다임의, 아키텍쳐/회로/소자/소재 기술이 집약된 초저전력 반도체 기술을 개발하는 사업을 추진함으로써 초연결사회 도래에 대비

- 초저전력 미래반도체 연구단은 국내 관련 연구역량을 총결집하여 차세대 기술을 효율적으로 개발하고, 대한민국 주도의 글로벌 연구컨소시움 구성을 주도함으로써, 미래기술개발 주도권을 선점하기 위한 top down 방식으로 사업추진

- 1단계 사업종료 시점인 2022년까지 현재의 경쟁기술대비 에너지 소비가 1/1000 이하인 초저전력 미래반도체 원천기술의 실현가능성을 검증하고, 2단계 사업기간( 2023-2025년)에는 민간기업 투자를 추가하여 기술선도형 제품을 구현

## 1.3. 사업기획 추진 목적

- "초저전력 미래 반도체 연구단"을 기획함에 있어, 사업의 주요개념 및 특징, 사업추진 전략 및 체계, 중점 연구개발 추진분야 후보군(Pool) 도출, 그리고 기대성과와 파급효과를 체계적으로 분석하여 사업의 성격과 예상성과물(Deliverable)을 명확히 제시함

- 기획 연구의 구체적인 목표

- 초저전력 미래반도체 응용기술 현황 분석 및 사업 기본방향 제시

- 국내외 초저전력 미래반도체 관련 기술개발 및 투자 현황 조사·분석

- 사업의 필요성과 핵심내용, 주요특징(타사업과의 차별성)을 정리

- 기술 추세 분석 및 산업동향 분석을 통한 사업방향 제시

- 글로벌 환경변화, 국내외 시장 및 전망, 국내 연구개발 인프라, 정부 정책현황 등의 분석을 통한 연구투자의 필요성 및 제반 연구개발 환경 파악

- 핵심 이슈 발굴 및 전략적 선택을 통해 세분화된 사업 추진전략 제안

- 사업 세부 추진계획 수립

- 사업의 개념(비전 및 목표 포함) 및 추진전략 수립

- 중점지원분야 등 기술개발의 세부 추진전략 수립

- 국내 연구 역량 및 자원을 토대로 10~15년 이내에 상용화가 가능하며, 세계 최고 수준의 경쟁력을 갖춘 ''초저전력 미래반도체 원천기술' 개발 전략 도출

- 사업 추진체계, 운영관리 및 평가, 리스크 관리 방안 등 사업체계 수립

- 소요예산 추정 근거제시, 총 사업비 및 기술별·연도별 소요예산 산출

- 사업 추진의 타당성 및 파급효과 도출

- 사업의 특성과 우리나라 산업에 미치는 기여도 분석을 통한 기획대상의 중점분야 의 연구투자 중요도 파악

- 사업 추진의 타당성, 시의성, 필요성 분석, 국고 지원의 필요성

- 상위계획과의 부합성, 기존 사업과의 차별성 및 연계성, 기술개발계획의 적절성 및 성공가능성, 사업추진 상의 위험요인 및 대응방안 등

- 사업의 파급효과 분석(경제적 파급효과 분석(비용-편익 분석),경제사회적 파급효과 분석, 과학기술적 파급효과 분석 등)

- 국내 연구 역량 및 자원을 토대로 10~15년 이내에 상용화가 가능하며, 세계 최고 수준의 경쟁력을 갖춘 ''초저전력 미래반도체 원천기술' 개발 전략 도출

- 시스템 레벨에서의 성능검증을 위해 기술시현 대상 시스템 및 관련 시장 동향 분석 및 사업 추진 타당성 근거 확보

- 원천특허 확보를 위한 특허전략 지원체계 구축방안 도출

- 사업 추진에 필요한 정책적 타당성을 분석하고, 본 사업 추진 이외의 대안에 대한 면밀한 검토 후에 DEA (Data Envelope Analysis) 분석기법에 의거 비용-효과 분석을 시행함으로써 본 사업의 추진 타당성을 확보

# 1.4. 사업기획 추진체계

- 총괄지원기관 (한국연구재단) 역할

- 사업추진방향 수립 및 관련 정책 협의 조정

- 사업기획내용(WG 1, 2)에 대한 검토 및 자문

- 사업 추진위원회 구성 및 추진사업에 대한 협의 및 의견조율

- WG (Work Group)의 구성 및 역할

- 사업추진전략 및 추진체계, 사업운영방안 등 상세기획

- 예비타당성 평가과정에서 대응이 필요한 사안에 대한 자문 수행

- 논문/특허분석 자문 수행

- 소자기술, 집적플랫폼/시스템융합 기술, 인프라개발, 기술사업화, 국제협력의 5개 분과와 자문위원회를 구성

- 각 분과에서 세부추진 아이템에 대한 수요조사 및 상세기획

- 자문위원회에서 추진전략 및 세부추진 아이템 수립에 대한 자문 수행

그림 1.3. 사업 추진 체계

# 1.5. 사업기획 추진경위

- 2014년 기초원천연구 기획과제 초절전고성능정보소자기술 개발 방안 연구를 통해 나노기술연구의 성과를 반도체 기술에 접목함으로써 기존 반도체 연구의 한계를 돌파 하기위한 기초연구전략 및 로드맵을 수립

- 2015년 나노소재원천기술 기획사업(초절전고성능 나노소자기술개발 추진방안) 결과로 제시된 "5대 초절전 나노소자기술 및 연관 소재/공정기술 고도화"를 이루기 위해 정부 지원투자효과가 높은 중·장기 연구 분야의 R&D 투자 계획 수립

- 제4기 나노종합발전계획상 미래이슈해결형 핵심전략과제 중 하나인 "극단적 에너지 절 감형 나노정보소자 기술"을 체계적으로 개발하기 위해, 2016년 추진 또는 계획 중인 사업을 검토함

- o 초저전력 미래반도체 기술로 명칭변경

- 제4기 나노종합발전계획수립 시 초저전력 미래반도체 기술을 4대 나노챌린지 프로젝트중의 하나로 선정하고, 사업추진을 위한 예산을 확보하기 위해 예비타당성 평가를 추진하기로 결정함

### ■ 사전기획 추진내용

| 날짜       | 추진내용                                        |

|----------|---------------------------------------------|

| 9월 12일   | 연구팀 구성 및 kick off meeting (한양대, 9월 16일)     |

| 9월 19일   | 1차 Webex meeting (과제 추진 현황 논의)              |

| 9월 29일   | 미국 현지 조사: U.C. Bekeley-T.J.King-Li          |

| J = 2J = | 교수면담,Stanford대-P.Wong 교수 면담)                |

| 9월 30일   | 미국 현지 조사: Monolithic 3D 사 방분 -Zvi Orbach 사장 |

| 3 설 30 현 | 면담,Apllied Materials — Director G.Lee 박사면담  |

| 10월 2일   | 2차 Webex meeting (과제 추진 현황 논의)              |

| 10월 16일  | 1차 웍샵 (판교, 반도체 연구조합), 6명의 소자 특허전문가 초청강연     |

| 10월 24일    | 3차 Webex meeting (과제 추진 현황 논의)         |

|------------|----------------------------------------|

| 11월17-1일   | ENGE 참석 및 해외 전문가 면담                    |

| 12월 12일    | Qualcomm 전문가 면담(강승혁, 송승철)              |

| 12월 14일    | LETI 주최 Workshop 참석                    |

| 12월 14일    | SEMATECH 주최 Workshop 참석                |

| 12월 16일    | Applied Materials 주최 workshop 참석       |

| 12월 28일    | 초저전력 미래반도체 나노전자기술예타기획 1차 회의            |

| 1월 15일     | 4차 Webex (나노인프라과제 활용 시범사업 추진논의)        |

| 1월 19일     | 과제 추진전략 점검 회의                          |

| 2월 4일      | 초절전 고성능 나노전자소자 기술개발 전략 검초 웍샵           |

| 2월 10일     | 초절전 고성능 나노전자소자 기술개발 전략 공청회             |

| 2월 18일     | 4차 나노종합발전계획 공청회 보완결과 자문회의              |

| 2월 19일     | 한-EU 화상회의 (Cluster간 협력논의)              |

| 3월 3일      | 미국 NRI 과제(E2CDA) 협력 의사 간접전달 (IBM VP)   |

| 3월 23일     | 초저전력 미래반도체 나노전자기술예타기획 2차 회의            |

| 4월 8일      | 초저전력 미래반도체 나노전자기술예타기획 3차 회의            |

| 4월 22일     | 초저전력 미래반도체 나노전자기술예타기획 4차 회의            |

| 4월 28일     | 예타기획팀 운영회의 (제주 라마다 호텔)                 |

| 5월 11일     | 초저전력 미래반도체 나노전자기술예타기획 5차 회의            |

| 5월 25일     | 초저전력 미래반도체 나노전자기술예타기획 6차 회의            |

| 5월 18일     | 초저전력 미래반도체 나노전자기술예타기획 7차 회의            |

| 7월 1-2일    | 예타보고서 작성 및 리뷰                          |

| 7월 6일      | 16년도 하반기 예비타당성조사 대상사업 기술성 평가 실시 설명회 참  |

| 7 2 0 2    | 석 (대전 인터시티 호텔)                         |

| 7월 15일     | 초저전력 미래반도체기술 개발사업단 예타기획 공청회 (일산 킨텍스,   |

| 7 2 10 2   | 나노코리아 기간중 개최)                          |

| 8월 3일      | 예비 타당성 과제 유치를 위한 과제 설명회 참석 (과천, 미래창조과학 |

|            | 부)                                     |

| 8월 9-10일   | 예타기획과제 기술성평가 및 후속 조치계획 논의              |

| 8월 20-21일  | 초저전력 미래 반도체 기술개발 사업 평가 부처 의견서 작성 회의    |

|            | (한양대학교)                                |

| 10월 6-7일   | 한-EU 나노웍샵 참석 및 사업 홍보                   |

| 10월 18-19일 | 초저전력 소자기술 해외전문가 전문가 초청웍샵 공동개최 (한양대학    |

|            | 교)                                     |

| 11월 18-20일 | 예타기획보고서 수정을 위한 워크샵 참석 (더케이호텔)          |

| 1월 11-12일  | 미래부 예타기획 경과보고 및 나노기술연구회 예타기획 관련 미팅     |

| 1월 15일     | 예타기획과제 최종보고서 작성을 위한 준비회의               |

| 예정         | 최종보고서 검토의견서 반영을 위한 회의                  |

| 예정         | 최종보고서 검토 및 자문회의                        |

| 예정         |                                        |

# 2. 국내외 환경분석

## 2.1 초절전 ICT 산업동향

## ■ 시장 환경 분석

- 차세대 ICT 기기 (사물 인터넷, 스마트폰, 스마트 워치 등 웨어러블 기기, 임플랜터블 기기, 초절전 고성능서버, 데이터 센터 등)와 관련된 <u>미래산업경쟁력은</u> 초저전력 나노소자기술이 결정하게 될 것임

- 인텔은 저전력 서버 시장의 95%를 선점한 상태임

- 저전력 반도체는 이미 전체 반도체 시장 중 가장 큰 시장을 형성

표 2.1. 세계 반도체 시장 규모 (자료: WSTS Forecast 2015 Fall, 단위: 백만달러)

|  |      | 201         | 14    | 201     | .5    | 201     | 6     | 201     | 7     |

|--|------|-------------|-------|---------|-------|---------|-------|---------|-------|

|  |      | 금액          | 비중    | 금액      | 비중    | 금액      | 비중    | 금액      | 비중    |

|  | 반도체  | 335,84<br>3 | 100.0 | 336,392 | 100.0 | 341,011 | 100.0 | 351,596 | 100.0 |

|  | 메모리  | 79,243      | 23.6  | 78,450  | 23.3  | 75,889  | 22.3  | 78,539  | 22.3  |

|  | 로직   | 91,633      | 27.3  | 90,212  | 26.8  | 91,753  | 26.9  | 93,785  | 26.7  |

|  | 아날로그 | 44,365      | 13.2  | 45,483  | 13.5  | 47,027  | 13.8  | 48,953  | 13.9  |

- 초저전력 미래반도체 적용제품의 시장규모는 메모리와 로직반도체 시장의 30 % 정도로 추정가능 (2017년 기준 51,697M\$ (약 62조), 2025년 추정치 76,380M\$ (약 91조, 환율 1\$=1200원, CAGR 5%가정))

- 이 시장은 현재 한국의 반도체 산업의 규모를 2배 이상 성장시킬 수 있는 규모임

## 2.1.1. 초저전력 반도체

## ■ 산업개요

- ICT 기술이 flexible, wearable 기반으로 발전해가면서, 사용시간을 연장하기위한 초저전력 반도체 제품 시장이 확대되어 가고있음

- 이에 따라, 반도체기술이 미세화에 의한 제조비용감소, 성능개선 패러다임에서 성능을 어느정도 유지하면서 소모전력을 저감하기위한 방향으로 발전해가고 있음

#### 그림 2.1 배터리에 기반 한 전자기기의 사용 예시

#### ■ 시장동향

- 사물인터넷(IoT) 시장을 대비해 반도체 제조사간 최소 전력의 마이크로컨트롤러 (MCU) 개발 경쟁이 치열함. 소형기기에서는 높은 성능보다 낮은 소비전력이 더 요 구되는데다 MCU를 장착하는 새로운 기기가 폭발적으로 늘어날 것으로 전망되기 때문임.

- 시장조사업체 IC인사이트는 지난해 세계 MCU 시장이 6% 늘어난 161억달러로 사상 최대 규모로 성장할 것으로 전망. 연평균 4.6% 성장해 오는 2018년 191억달러 시장 형성이 전망됨.

그림 2.2 마이크로컨트롤러(MCU) 개발 역사와 예측

## ■ 국내 관련 산업동향

- 국내 TI코리아는 동작전력 95mA, 대기전력 850nA 소모에 그치는 저전력 32비트 MCU출시. 아날로그디지털컨버터(ADC)를 포함해 전력 효율성과 성능을 더 개선했음.

- MCU 시장 강자인 ST마이크로일렉트로닉스(스위스)도 초저전력 MCU 기술과 제품 개발에 속도를 내고 있으며, MCU 내외부 메모리가 대기 상태 없이 작동할 수 있는 독자 기술로 유효전력 100μA/Mb을 구현했음. (정지·대기 모드, 소비 전류가 30nA에 불과한 셧다운 모드를 제공).

- 초저전력 반도체 업체인 퀵로직(미국)은 한국 지역에 지사를 설립. 아시아 지역에서 모바일 기기의 폭발적인 성장을 고려할 때, 한국은 매우 중요한 전략적 요지라는 판 단임.

- 퀵로직은 모바일 기기용 초저전력 센서 허브 솔루션 플랫폼을 출시. 이 플랫폼은 소비 전력을 시스템 전력의 약 1% 수준으로 절감하여 센서 관리와 퓨전 기능을 통합하고 애플리케이션 프로세서 통신을 최적화하며 상시 상황 인식을 지원함.

- 현 세대 스마트폰에서는 일반적으로 마이크로컨트롤러/마이크로프로세서에서 실행되는 소프트웨어 또는 고정 기능 ASSP(특정 용도 표준 제품)를 사용하여 센서 퓨전 기능을 구현함. 하지만, 마이크로컨트롤러 또는 마이크로프로세서 기반 솔루션은 배터리 수명에 미치는 영향을 1% 미만으로 유지할 만큼 저전력으로 작동하지않기 때문에 비용, 크기, 무게에 있어서 상당히 불리함.

- 퀵로직은 프런트 엔드 센서 관리를 위한 마이크로 코드형 상태 기계와 실시가 센

서 데이터 처리를 위한 초저전력 CISC(복잡 명령 집합 컴퓨터) 기반 ALU(산술 논리 연산 장치), 재프로그래밍이 가능한 내장형 논리를 결합한 새로운 개념의 센서 허브 아키텍처를 개발했음. 센서 데이터를 실시간으로 관리하고 연산하는 데 따른 스마트폰 애플리케이션 프로세서의 작업 부하를 해소함으로써, 모바일 기기의 차세대 센서 활용 사례, 즉 상시 상황 인식 기능을 지원할 수 있는 수준의 소비 전력을 실현함. OEM과 써드 파티 소프트웨어 개발자들은 걸음 수 집계 및 기타 건강/운동모니터링, 보행자 항법 장치/실내 네비게이션, 소비자 행동 분석, 타깃 광고, 실시간스포츠 데이터 수집, 증강 현실 등 상시 상황 인식 기능을 필요로 하는 무수한 응용 사례를 실현 가능해짐.

- 향후 스마트폰 시장은 MEMS 분야에서 가장 크고 빠르게 성장하는 시장이 될 것이라는 전망 하에, 2016년이면 모든 스마트폰과 태블릿에 가속도계, 자기계, 자이로스코프와 같은 내부 MEMS 센서가 탑재될 것으로 예측됨. 이러한 센서와 배터리 소모를 최소화하면서 상시 상황 인식이 센서 허브 기술에 결합된다면 새로운 서드 파티애플리케이션이 개발 가능함.

- 미국 아이와트가 자사 제품 중 가장 빠른 대기 전력 모드 회복 성능의 2개의 파워어댑터 칩셋을 포함한 펄스폭 변조 (PWM) 컨트롤러 제품 라인업을 확대했다. 이 칩셋들은 각각 최대 12와트 출력 전력에서 10mW 이하의 초저대기 전력과 24W의 출력 전력에서 20mW 이하의 대기 전력을 달성. 차세대 미디어 태블렛과 스마트폰의유니버설 AC/DC 어댑터 및 충전기뿐 아니라, 플러그인 상태에서 대기 전력 모드로남아있는 소비가전 기기와 홈네트워킹 기기에게 적용가능함.

- 미국 엔비디아는 CES 2015에서 발표한 '테그라X1'의 후속 모델을 선보일 것으로 전망됨. 테그라 X1은 256코어 맥스웰 그래픽칩(GPU)와 64비트(bit) 옥타코어 CPU가합쳐진 것으로 1초당 1조회의 연산이 가능한 프로세서임. 엔비디아는 이 칩을 자율주행차용으로 내놓았음.

- 엔비디아는 독자적인 자율주행차 기술도 개발중임. 구글(미국)의 자율주행차는 라이다(LIDAR·레이저를 발사해 주변 지형이나 장애물과의 거리를 측정하는 장비)를이용해 주변 상황을 판단하고 운행함. 반면, 엔비디아의 자율주행차 기술은 라이다장비 없이 차량에 부착된 12대의 인공지능 카메라가 촬영한 영상을 분석해 차를운전함. 즉, 실시간으로 들어오는 영상을 종합하고 분석해야 하는 만큼 고성능 프로세서가 필수적임.

- 웨어러블 등 디지털 헬스기기에 들어가야 하는 칩 또한 크기가 작으면서 전력 소모는 적어야 함. 더불어, 심장 박동수 등을 정확하게 측정할 수 있도록 정교해야 함. 최근, 초저전력 반도체 전문업체인 퀵로직은 심박수 측정, 숙면 감지등에 이용할 수 있는 제품을 전시함.

### 2.1.2. 초절전 Microprocessor

#### ■ 산업개요

- 세계 ICT 환경은 90년대 PC, 2000년대 스마트폰 기반의 모바일 환경에서 IoT, wearable 등으로 변화하고 있으며, 산업 전반에 막대한 영향을 미칠 것으로 예상됨.

- IoT 시대의 반도체는 극단적인 저전력 소모를 요구되고 있음. 기존 CMOS 반도체의

경우 지속적인 미세화에 의해 기하급수적으로 전력밀도가 증가되고 있음.

○ 이러한 환경 변화에 의해 반도체의 패러다임이 성능 일변도에서 저전력으로 변화하고 있음.

## ■ 시장동향

○ 시장조사기관 가트너(Gartner)는 2015년 전 세계 반도체 시장이 전년대비 4.0% 증가한 3.540억 달러에 이를 것으로 전망함.

○ 2015년 성장 기여도 측면에서 스마트폰용 반도체의 기여율이 81.1%로 높게 나타남. 이는 지난 20년간 PC 시장이 견인했던 반도체 시장이 축소되고 저전력이 요구되는 스마트폰용 반도체 시장의 성장이 주도되고 있음을 의미함.

< Source : Gartner (2015. 5) >

#### 그림 2.4 전자 기기별 반도체 시장 동향

#### ■ 산업동향

- 영국 ARM Holdings사에서는 만들어서 출시되는 CPU 아키텍처 시리즈인 ARM 프로세서는 Intel 사의 x86 시리즈에 비해 더 낮은 성능을 보이고 있지만, 소비 전력이 낮은 장점이 있어 전력소모가 중요한 테블릿 PC나 스마트 폰의 AP로 ARM 아키텍처가 많이 사용되고 있음. ARM Holdings사는 팹리스 업체임으로 퀄컴, 삼성전자, 애플, NVIDIA 등 많은 업체에서 이 아키텍처를 이용하여 제품을 생산하고 있음.

- Intel사는 스마트폰, 태블릿 PC 등의 AP로 아톰이라는 프로세서 모델을 생산하여 저 전력 프로세서를 개발하고 있음.

## 2.1.3. 초절전 센서구동칩

### ■ 산업개요

- ICT 기술이 발달함에 따라 저전력, 초소형 센서노드를 설치하여 무인으로 정보를 얻을 수 있는 시스템 도입이 점차 확대되는 추세임

- 이를 위해 온도, 습도, 가스 등 다양한 환경 정보를 획득할 수 있는 센서 뿐만 아니라. 초소형 저전력 복합환경센서 ROIC (Read-Out IC)의 중요성이 증가됨.

## ■ 시장동향

○ 세계 센서 시장은 2014년 795억 달러에서 2019년 1,161억 달러로 연평균 7.9%의 성장률을 보이며 성장할 전망임.

표 2.2 세계 센서 시장 동향

<source : BCC Research>

○ 국내 시장은 산업통상자원부의 보도에 따르면, 2012년 약 54억 달러 규모에서 2020 년 99억 달러 규모로 연평균 10.4% 성장할 것으로 전망됨.

표 2.3 국내 반도체 시장 전망

<Source : 지식경제부(2012)>

○ 국내 수요기업은 국내 제품의 신뢰성, 첨단 센서의 성능 등의 문제로 센서 수요를 해 외에서 주로 조달함.

#### ■ 산업동향

- 세계 센서 산업은 IT 융합의 진전으로 센서 사용이 급증하고 센서의 첨단화 추세에 따라 시장이 급성장 하고 있으나, 국내 산업의 경쟁력은 매우 취약한 상태임.

- 국내 기업은 첨단 센서에 대한 기술력 부족과 일반 센서의 가격경쟁력 취약으로 인해 미국, 독익, 일본 등 선진기술 보유국과 가격경쟁력을 앞세운 중국의 중간에 위치한 샌드위치 상태임

- 센서 기술은 미국, 독일 등 일부 선진국을 중심으로 디지털 센서 단계를 지나 스마트 센서에 대한 연구가 활발하게 진행되고 있으며, 첨단 센서의 경쟁력을 타산업분야의 경쟁력의 핵심으로 인식하여 집중 지원하고 있음.

## 2.2 초절전 ICT 연구 개발 동향

## 2.2.1 Silicon 기반 소자연구

- 실리콘 기반 반도체소자 기술개발 현황

- 1960년대에 처음으로 실리콘 (Si) 및 실리콘 산화막 (SiO₂)을 기반으로 하는 MOSFET (Metal Oxide Semiconductor Filed-Effect-Transistor, 이하 소자)이 개발된 이래로, 반도체 칩 성능 (Performance) 향상을 위해 소자 크기를 줄이고 반도체 칩 단위 면적당 들어가는 소자의 개수를 증가 시키는 방향으로 연구가 진행됨 (칩 집적도 향상).

- 무어의 법칙 (Moore's Law)에 따라 매 2년마다 소자의 미세 선폭이 약 70% 수준으로 감소하는 지속적인 소자 스케일링 (Scaling)이 이루어졌고, 2003년도에는 처음으로 100nm 이하 수준의 90nm급 트랜지스터가 상용화됨.

- 2012년에는 Intel에 의해 2차원 평면 구조의 트랜지스터에서 벗어난 3차원 구조의 22nm FinFET이 등장하였고, 이후로도 소자의 스케일링은 지속적으로 이루어져 14nm를 넘어 현재는 10nm 미만의 트랜지스터 상용화 연구까지 진행 중임.

그림 2.5. 트랜지스터 혁신 개발 동향 (source: Intel)

#### ■ 실리콘 기반 반도체소자의 문제점: "발열문제"

- 소자의 스케일링은 꾸준히 이루어져 반도체 칩 (Chip) 하나에 들어가는 소자의 개수는 지속적으로 증가한 반면, 소자를 구동시키는데 드는 구동전압 (Power supply voltage, V<sub>DD</sub>)의 스케일링은 **Boltzmann limit이라고 불리는 물리적 한계** 때문에 소자의 사이즈에 비례하여 적절하게 줄어들지 못함.

- 결과적으로, 구동전압 스케일링 한계로 반도체 칩의 소모전력  $(P \propto V_{DD}^2)$  은 지수함수적으로 증가하게 되어 적절하지 못한 대안이 없으면 발열량은 핵원자로  $(Nuclear\ Reactor)$ 에서 발생하는 수준까지 예상됨.

- 2020년도에는 칩 하나에 들어가는 소자의 개수가 약 500억 개까지 증가할 것으로 추정되고 있으며, 앞으로의 발열문제는 더욱 심각해질 것으로 예상됨.

- 세계 반도체 기술개발의 로드맵을 제공하는 ITRS 또한 2015년 발표 자료에서

"Energy Crisis on Chip"이라는 표현을 사용할 정도로 발열 문제를 심각하게 고려하고 있으며, switching energy를 감소시키는 것을 차세대 반도체 소자의 핵심기술 목표로 잡음.

그림 2.6. CMOS 기술이 직면한 발열문제의 실태 (Source: Bernard S. Meyerson (IBM)) (왼쪽)와 IoT 시대의 반도체소자 개수 추이예상도 (Source: Connect Blue 사 내부기술보고서 2014) (오른쪽)

## 2.2.2 초저전력 미래반도체 소자 연구

### ■ 기술 환경 분석

- 해외 경쟁국들은 2013년부터, 미세화 기술의 한계를 극복하기 위한 대안 기술에 대한 논의 확대하여, 종래의 고성능 중심 기술에서 저전력 기술 제품으로 시장주도 기술이 바뀌어가고 있음

- IBM, LETI등에서 신소재 기반 신소자 기술, Cool cube등 신기술 제시

- 특히 미국과 유럽에서 연구의 필요성에 대해 활발히 논의되고 있으나, 실제 소자를 연구하는 과제는 아직 프로그램 제안 단계임. 과제요청서를 기준으로 판단한다면, 구체적인 전략이나 로드맵을 확보하지는 못한 상태인 것으로 판단됨

표 2.4. 미국과 유럽의 초절전 기술 관련 프로그램

| 국<br>가 | 연구프로그램                                                                                 | 연구내용                                                                                                        | 비고                    |

|--------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|

| 미<br>국 | E2CDA (Energy<br>efficient computing for<br>devices and<br>architectures)<br>연 48억/ 3년 | <ul> <li>초절전 신소자 기술과 아키텍쳐에 대한 과제 수행 예정 (현재 제안서 접수중)</li> <li>아직 구체적인 전략이 있는 것이 아니라 기술탐색을 주목적으로 함</li> </ul> | 2016년<br>하반기<br>시작 예정 |

| 유립     | ICT-31:                                                                                | - 3차원 집적기술, 뉴로모픽 아키텍<br>쳐등 전력절감형 기술공모                                                                       | 2017년<br>1월 시작        |

| microelectronics<br>연 50억/ 5년 | - 상용화 전망에 대한 계획 부재 | 예정 |

|-------------------------------|--------------------|----|

|-------------------------------|--------------------|----|

- IoT의 경우 단위소자의 연구 이외에 TSV/M3D 등 소자 융합과 저전력을 위한 연구를 동시에 진행하고 있으며, 초저전력 시스템 구현을 위해 연산 아키텍쳐/회로/소자/소재에 대한 초대형 연구사업 시작됨

- Qualcomm-LETI(프)-SMIC(중)-북경대 등 공동개발 진행

- 뉴로모픽의 경우 미, EU, 일본을 합쳐 2조원 정도가 투자되고 있음

- 반면 국내 민간부분의 연구는 아직 DRAM/Flash memory 등 메모리 소자의 미세화와 미세화 관점에서의 대체 소자 (STT MRAM, RRAM)로 집중되어 있음

- 또한 국내의 저전력 융합 소자, IoT 등 초연결 사회에 대비한 기반 연구는 매우 부족함 뉴로모픽 소자기술은 미래융합파이오니어 사업에서 일부 진행 중

- ICT 초연결 사회를 위한 scaling 접근방식이 아닌 flexibility를 갖는 다양한 제품군이 부재하며 또한 이를 구현할 소자, 재료, 공정 및 후방기술 미비한 실정임

- 국내 팹리스 기업은 연구개발 분야 투자가 미약하여 팹리스 기업이 2011년 연구개발에 투자한 비용은 48억 원으로 매출액 대비 0.32%에 불과함

- 지속적인 연구개발로 신기술과 신제품을 확보해야 기업이 경쟁력을 갖출 수 있는 구조임에도 불구하고 기업 대부분의 규모가 영세하여 연구개발이 적극적으로 이루 어지지 못하고 있음

- 또한 중소기업의 제품 수준이 글로벌 기준에 미달되어 대기업과의 협력관계를 형성할 기반이 약함`

#### ■ ITRS Emerging Research Devices (ERD)

그림 2.7. 차세대 유망 반도체 소자 연구분야 모식도 (Source: ITRS 2015)

○ ITRS 2015에서는 차세대 소자 연구(Emerging Research Devices) 방향을 위의 같이 분류하고 있으며, 특히 초절전 반도체 로직 소자(Emerging Logic Devices) 연구와

관련해서는 크게 다음의 두 방향을 잡음.

- 1) 기존 CMOS 스케일링 기술을 확장한 "CMOS Extension" 기술

- 고성능 모빌리티 채널 물질 활용을 통한 on current 향상 (e.g., Ⅲ-V, Ge, Graphene, Carbon Nanotube(CNT))

- 게이트의 효율적 채널 컨트롤성을 확보하기 위한 비평면형(non-planar) 소자 구조 (e.g., FinFET, Gate-all-around FET(GAAFET) 등)

- 2) 새로운 동작 메커니즘을 활용한 "Beyond CMOS" 기술

- 전하 기반 (e.g., TFET, NCFET, NEMS, Mott-FET 등)

- 비전하 기반 (e.g., SpinFET, Nano-magnetlogic(NML), Spin wave logic)

- 위의 두 기술은 전하/비전하 기반(Charge/Non-charge-based) 축과 기존/신 구조/물질(Conventional/Novel Structure/materials) 축으로 나눌 때 아래의 표와 같이 정리됨.