반도체분야 미래유망 핵심기술확보를 위한

신규 대형 중장기 R&D 프로그램 기획연구

한국반도체연구조합

한국연구재단

# 제 출 문

한국연구재단 이사장 귀하

본 보고서를 “반도체분야 미래유망 핵심기술확보를 위한 신규 대형 중장기 R&D 프로그램 기획연구”의 최종보고서로 제출합니다.

2018. 5.

## < 목 차 >

---

|                                  |     |

|----------------------------------|-----|

| 제1장 추진배경 및 필요성 .....             | 1   |

| 1.1 개념 및 특성 .....                | 1   |

| 1.2 기술개요 .....                   | 4   |

| 1.3 기술개발 필요성 .....               | 8   |

| 제2장 4차 산업혁명시대의 특징 및 주요국 동향 ..... | 13  |

| 2.1 개요 및 특성 .....                | 13  |

| 2.2 주요국 동향 .....                 | 15  |

| 제3장 지능형 반도체 기술 개발사업 .....        | 19  |

| 3.1 국내외 기술개발 동향 .....            | 19  |

| 3.2 시장동향 .....                   | 80  |

| 3.3 국내외 정책동향 .....               | 105 |

| 3.4 특허분석 .....                   | 112 |

| 3.5 국내 역량분석 .....                | 116 |

| 3.6 기존 R&D 분석 .....              | 123 |

| 제4장 개발 목표 .....                  | 128 |

| 4.1 개발목표 및 내용 .....              | 128 |

| 4.2 개발 내용 .....                  | 129 |

| 4.3 개발 기간 및 소요예산 .....           | 137 |

| 제5장 추진 전략 및 체계 .....             | 140 |

| 5.1 추진 전략 .....                  | 140 |

| 5.2 추진 체계 .....                  | 143 |

| 5.3 추진 근거 .....                  | 152 |

|                         |     |

|-------------------------|-----|

| 제6장 개발기간 및 소요예산 .....   | 161 |

| 제7장 타당성 분석 및 기대효과 ..... | 162 |

| 7.1 정책적 타당성 .....       | 162 |

| 7.2 기술적 타당성 .....       | 168 |

| 7.3 경제적 타당성 .....       | 171 |

| 7.4 기대효과 및 파급효과 .....   | 182 |

| 부록1. 기획위원회 명단 .....     | 183 |

| 부록2. 기술수요 조사표 .....     | 185 |

| 부록3. 기술수요 조사 리스트 .....  | 309 |

## < 표 차례 >

---

|                                             |    |

|---------------------------------------------|----|

| <표 1> 새로운 미국혁신전략의 주요 내용                     | 15 |

| <표 2> 제 4차 산업혁명에 대한 일본정부의 7가지 대응방침          | 16 |

| <표 3> 중국의 인공지능 정책 방향                        | 18 |

| <표 4> 주요국의 4차 산업혁명에 대한 대응전략 비교              | 18 |

| <표 5> 국내 프로세서 관련 기술 개발 실적                   | 24 |

| <표 6> 자율 주행을 위한 NVIDIA의 프로세서 기반 시스템         | 26 |

| <표 7> 신경세포 모방소자 국내 연구 개발 동향                 | 49 |

| <표 8> 신경세포 모방소자 국외 연구동향                     | 50 |

| <표 9> 국내 음성기반에 지능형 IoT 서비스                  | 56 |

| <표 10> 개방형 플랫폼 관련 협의체 현황 및 기술현황             | 62 |

| <표 11> 인텔리전트 엣지 단말 운영체제                     | 64 |

| <표 12> 글로벌 기업들의 AI 확보를 위한 플랫폼 사례            | 65 |

| <표 13> 글로벌 기업들의 기술력 확보를 위한 인수사례             | 67 |

| <표 14> 국내 팹리스와 파운드리 기업의 관계                  | 68 |

| <표 15> 세계 인공지능 시장                           | 81 |

| <표 16> 지역별 인공지능 시장                          | 81 |

| <표 17> APAC지역 국가별 인공지능 시장                   | 81 |

| <표 18> 세계 Microcomponent 시장 전망              | 82 |

| <표 19> Microprocessor Embedded 지역별 시장       | 82 |

| <표 20> 아태지역 Microprocessor Embedded 세계시장 비중 | 82 |

| <표 21> 세계 뉴로모픽 칩 시장                         | 84 |

| <표 22> 지역별 뉴로모픽 칩 시장                        | 84 |

| <표 23> 아태지역 뉴로모픽 칩 시장                       | 85 |

| <표 24> 한국의 뉴로모픽 칩 세계시장 비중                   | 85 |

| <표 25> 세계 인지 소프트웨어 시장                       | 86 |

| <표 26> 세계 AI-Driven Hardware 시장             | 86 |

|                                                 |     |

|-------------------------------------------------|-----|

| <표 27> 지역별 AI-Driven CPU 시장                     | 86  |

| <표 28> 아태지역 AI-Driven GPU Chip 세계시장 비중          | 87  |

| <표 29> 지역별 AI-Driven GPU Chip 시장                | 87  |

| <표 30> 아태지역 AI-Driven GPU Chip 세계시장 비중          | 87  |

| <표 31> 세계 3D IC 시장                              | 87  |

| <표 32> 지역별 모노리식 3D IC 시장                        | 88  |

| <표 33> 아태지역 모노리식 3D IC 세계시장 비중                  | 88  |

| <표 34> 기술 분야별 인공지능 관련 매출액 전망                    | 89  |

| <표 35> 낸드 플래시 응용 제품 시장 규모                       | 93  |

| <표 36> 저장 솔루션 시장 규모                             | 93  |

| <표 37> 세계 IoT 반도체 시장 실적 및 전망                    | 94  |

| <표 38> IoT 반도체 연도별 시장 성장률 전망                    | 95  |

| <표 39> IoT 반도체 분야별 마켓 규모                        | 95  |

| <표 40> 프로세서 분야 상세 시장 분석                         | 96  |

| <표 41> 서비스에 따른 프로세서 분야 상세 시장 분석                 | 96  |

| <표 42> IoT 반도체 시장별 규모 전망                        | 98  |

| <표 43> IoT 디바이스의 처리분야 반도체 매출 전망                 | 99  |

| <표 44> IoT 반도체 분야의 산업별 시장전망                     | 100 |

| <표 45> 국내 음성기반에 지능형 IoT 서비스                     | 101 |

| <표 46> IoT 반도체 차량 분야의 시장전망                      | 102 |

| <표 47> IoT 빌딩 오토메이션 분야의 시장전망                    | 102 |

| <표 48> IoT 빌딩 오토메이션 분야의 반도체 시장전망                | 103 |

| <표 49> Moonshot 요소기술                            | 106 |

| <표 50> 중국 주요 반도체산업 지원정책                         | 107 |

| <표 51> HBP의 연구내용                                | 109 |

| <표 52> HBP의 ICT 플랫폼                             | 109 |

| <표 53> 인공지능기술 R&D 예산 현황                         | 111 |

| <표 54> 시스템반도체 매출 상위 기업                          | 119 |

| <표 55> 글로벌 팹리스 기업과 국내 기업의 ‘16년 인력, 매출, R&D투자 비교 | 120 |

| <표 56> 인공지능 반도체 SWOT 분석                         | 121 |

|                                         |     |

|-----------------------------------------|-----|

| <표 57> 인공지능기술 R&D 예산 현황                 | 123 |

| <표 58> 반도체분야 주요사업 분석                    | 124 |

| <표 59> 전자정보디바이스사업 주요 투자분야               | 125 |

| <표 60> 시스템반도체상용화기술개발사업 주요 투자분야          | 125 |

| <표 61> 시스템반도체 분야 주요성과 과제                | 125 |

| <표 62> 공정장비 분야 주요성과 과제                  | 126 |

| <표 63> 시스템반도체상용화사업 주요성과 과제              | 126 |

| <표 64> 인공지능 반도체의 기술개발 내용 분류 및 단계별 목표    | 130 |

| <표 65> 인공지능 반도체 사업 연구비                  | 137 |

| <표 66> 반도체 설계 세부기술                      | 137 |

| <표 67> 반도체 소자·공정 세부기술                   | 138 |

| <표 68> 사업 추진방향                          | 141 |

| <표 69> 인공지능 반도체 사업단의 역할                 | 144 |

| <표 70> 인공지능 반도체 사업단의 주요역할               | 146 |

| <표 71> 기술이전 체계 개선                       | 151 |

| <표 72> 미래성장동력(산업엔진 포함) 19대 분야           | 154 |

| <표 73> 미래창조과학부 지능형반도체 2022 전략 핵심기술      | 158 |

| <표 74> 인공지능 반도체 사업 연구비                  | 161 |

| <표 75> 기존 사업과의 비교                       | 170 |

| <표 76> 지능형반도체 세계시장규모                    | 177 |

| <표 77> 세부추진과제별 시장점유율                    | 178 |

| <표 78> 편익분석 지표 요율 종합                    | 179 |

| <표 79> Cognitive Computing 연도별 편익 분석 결과 | 180 |

| <표 80> Intelligent Edge 연도별 편익 분석 결과    | 180 |

| <표 81> 반도체장비/재료 연도별 편익 분석 결과            | 181 |

| <표 82> 본 사업의 세부추진과제별 B/C 분석 결과          | 181 |

## < 그림 차례 >

---

|                                                  |    |

|--------------------------------------------------|----|

| <그림 1> 4차 산업혁명 혁신 서비스와 지능형 반도체 및 소프트웨어           | 2  |

| <그림 2> 지능형 반도체의 개념과 응용 분야                        | 3  |

| <그림 3> 인공지능 기술개발 역사와 지능형 반도체                     | 4  |

| <그림 4> Alan Turing                               | 4  |

| <그림 5> 인공지능 서비스가 요구하는 성능 및 전력 소모량                | 5  |

| <그림 6> 하드웨어 기반 인공지능 시스템                          | 6  |

| <그림 7> 지능형 반도체의 현재와 미래 혁신 방향                     | 9  |

| <그림 8> 4차 산업혁명 서비스를 기반으로 하는 지능형 반도체의 기술혁신 및 산업도약 | 12 |

| <그림 9> 딥 러닝이 적용된 뇌-컴퓨터 인터페이스                     | 21 |

| <그림 10> 딥러닝을 활용한 뇌신호 분석 (출처: 고려대학교 이성환 교수 연구실)   | 21 |

| <그림 11> ExoBrain 프로젝트 구성도 및 장학퀴즈 대결              | 23 |

| <그림 12> SW26010                                  | 25 |

| <그림 13> ADAS 기능 예                                | 26 |

| <그림 14> 파스칼 SM 아키텍처                              | 27 |

| <그림 15> Google의 TPU                              | 27 |

| <그림 16> Xavier Chip 구조 및 개발 보드                   | 27 |

| <그림 17> Snapdragon 835 Block Diagram             | 29 |

| <그림 18> 자동차용 Nauto                               | 29 |

| <그림 19> CEVA DNN의 동작 개념                          | 30 |

| <그림 20> Cambricon ISA 및 Pipeline Architecture    | 30 |

| <그림 21> Cambricon Chip Area & Power Summary      | 31 |

| <그림 22> Myriad2 칩과 SHAVE VLIW프로세서 구조             | 31 |

| <그림 23> Myriad 2 Software Stack                  | 32 |

| <그림 24> Neon과 Caffe간의 Computing Time 비교          | 33 |

| <그림 25> 애플의 A11 바이오닉스 프로세서                       | 33 |

| <그림 26> 화웨이의 Kirin 970                           | 34 |

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| <그림 27> 영상기반 객체인식용 인공지능신경망 층수 추세                                               | 34 |

| <그림 28> 최근의 인공지능용 하드웨어 시스템의 형태 및 소비 에너지                                        | 35 |

| <그림 29> Micron의 오토마타 프로세서                                                      | 36 |

| <그림 30> Venray의 TOMI (2012–2014)                                               | 36 |

| <그림 31> University of Illinois, Urbana–Champaign의 SRAM과 프로세서를 이용한 PIM          | 37 |

| <그림 32> University of California, Santa Barbara에서 개발한 DNN을 위한 ReRAM 기반의 PIM 구조 | 37 |

| <그림 33> Toshiba의 SRAM 혹은 ReRAM 기반의 PIM                                         | 38 |

| <그림 34> SRAM 타입의 CMOS 시냅스                                                      | 40 |

| <그림 35> Floating gate 타입의 CMOS 시냅스                                             | 40 |

| <그림 36> straintronic spin 뉴런의 형태                                               | 42 |

| <그림 37> ONN회로를 사용한 패턴인식                                                        | 42 |

| <그림 38> CMOL 회로 구현 형태                                                          | 43 |

| <그림 39> 상변화 메모리 소자를 시냅스로 사용한 패턴인식 시스템                                          | 44 |

| <그림 40> CMOS회로와 강유전체 맴리스터를 결합한 구조                                              | 44 |

| <그림 41> Hirerachical AER I&F Array 트랜시버                                        | 45 |

| <그림 42> Brains in Silicon 그룹의 NeuroGrid                                        | 46 |

| <그림 43> IBM의 True North 구성                                                     | 46 |

| <그림 44> 실시간으로 동작하는 다중 물체 인식 시스템                                                | 47 |

| <그림 45> University of Heidelberg의 HICANN 연상장치와 웨이퍼 scale 모듈                    | 47 |

| <그림 46> University of Manchester의 SpiNNaker 연산장치                               | 48 |

| <그림 47> ROLLS 뉴로모픽 프로세서와 물체인식 시스템                                              | 48 |

| <그림 48> General Vision, Neuromen                                               | 51 |

| <그림 49> Intel – Quark™ SE Micro-controller                                     | 51 |

| <그림 50> Qualcomm-NPU                                                           | 52 |

| <그림 51> Intel-Loihi                                                            | 52 |

| <그림 52> 인텔의 CNN 전용처리칩인 Arria10과 2세대 Quark Prime                                | 53 |

| <그림 53> 해외 멀티모달 센서 신호처리 연구의 예                                                  | 54 |

| <그림 54> 해외 멀티모달 System VLSI 연구 결과                                              | 54 |

| <그림 55> 멀티모달 정보를 이용한 클라우드 및 네트워크연결 시제품                                         | 55 |

| <그림 56> MCU기반에 음성기반의 API와 결합된 음성 인지 플랫폼                                        | 56 |

|                                                     |    |

|-----------------------------------------------------|----|

| <그림 57> RISC-V 오픈코어 지원 기업 및 오픈그룹들                   | 57 |

| <그림 58> RISC-V와 패리스                                 | 57 |

| <그림 59> PULPion 프로젝트의 개념도                           | 58 |

| <그림 60> Microsemi RISC-V IP 설계/검증용 FPGA 보드          | 58 |

| <그림 61> 아두이노와 이클립스 환경에서의 RISC-V                     | 58 |

| <그림 62> 삼성 ARTIK 플랫폼                                | 59 |

| <그림 63> OSI 단체에 소속된 오픈소스 멤버                         | 60 |

| <그림 64> 아두이노 재단의 ESLOV 응용 서비스 기술                    | 62 |

| <그림 65> 삼성 개방형 플랫폼 프로젝트 “SAMI”                      | 66 |

| <그림 66> 차세대 자동차를 위한 소형/저전력 Edge 기술                  | 69 |

| <그림 67> 시스템반도체 기본 구성 예시                             | 70 |

| <그림 68> 자동차용 시스템반도체 적용 예시                           | 71 |

| <그림 69> 차량용 반도체에 적용되는 AEC 신뢰성 표준규격                  | 72 |

| <그림 70> 고안전 시스템반도체의 구조(NXP, 차량용 레이더)                | 72 |

| <그림 71> Renesas의 ‘Smart Analog’의 개요                 | 74 |

| <그림 72> 웨어러블 삽입형 센서의 예                              | 74 |

| <그림 73> 초실감형 UX의 다양한 적용 분야                          | 76 |

| <그림 74> 초실감형 UX용 반도체                                | 77 |

| <그림 75> HMD 타입의 증강현실 장비의 예, 헐로렌즈(좌), 메타2(우)         | 77 |

| <그림 76> 국내 스마트폰 기반 VR 기기,LG 360 VR(좌), 삼성 기어 VR(우)  | 79 |

| <그림 77> 한국의 아시아 지역 인공지능 시장 점유율(2014) 및 주요 기술별 시장 전망 | 80 |

| <그림 78> 인공지능 산업 시장 규모 및 전망                          | 83 |

| <그림 79> 스마트기기 Hypercycle                            | 83 |

| <그림 80> 인공지능 기반 스마트 머신 시장 규모 및 전망                   | 84 |

| <그림 81> DRAM 시장 전망                                  | 90 |

| <그림 82> NAND시장 전망                                   | 90 |

| <그림 83> 2014 - 2020년 차세대 메모리 시장 전망                  | 90 |

| <그림 84> DRAM 제품군별 용량 점유율                            | 91 |

| <그림 85> 메모리 별 시장 전망                                 | 91 |

| <그림 86> 메모리 반도체 공급업체 매출비율                           | 92 |

|                                                     |     |

|-----------------------------------------------------|-----|

| <그림 87> (a) DRAM, (b) 낸드플래시 솔루션 별 용량 점유율            | 92  |

| <그림 88> IoT 반도체 시장 전망(센서 분야 포함)                     | 94  |

| <그림 89> 세계 IoT용 반도체 시장전망                            | 95  |

| <그림 90> IoT 반도체 및 센서 시장 전망                          | 97  |

| <그림 91> 국외 IoT 시장 규모(左), ICT 시장 규모(右)               | 97  |

| <그림 92> 국내 IoT 시장 규모 전망                             | 98  |

| <그림 93> 사물인터넷 응용 분야별 활용준비정도 및 성장성                   | 99  |

| <그림 94> 시스템반도체 산업구조                                 | 100 |

| <그림 95> 모바일 헬스 IoT 현황                               | 104 |

| <그림 96> Brain Initiative 추진체계                       | 108 |

| <그림 97> 일본 인공지능 R&D 추진체계                            | 110 |

| <그림 98> 국가별 특허 출원 추이                                | 112 |

| <그림 99> 기술별 특허 출원 추이                                | 113 |

| <그림 100> 국가별 인공지능 반도체 특허 출원 추이                      | 113 |

| <그림 101> 인공지능 세부기술별 특허 현황                           | 113 |

| <그림 102> 국가별 미래소자 특허 출원 추이                          | 114 |

| <그림 103> 미래소자 기술별 특허 현황                             | 114 |

| <그림 104> 국가별 메모리 솔루션 특허 출원 추이                       | 115 |

| <그림 105> 메모리 솔루션 세부기술별 특허 현황                        | 115 |

| <그림 106> 인공지능 반도체를 활용한 스마트카 핵심 기술에 대한 각 국의 기술별 점수비교 | 116 |

| <그림 107> Qualcomm Zeroth 데모                         | 117 |

| <그림 108> 지능형반도체 신사업 기술 트리                           | 129 |

| <그림 109> 초고속, 초저전력 반도체 기술 개발 개념                     | 135 |

| <그림 110> 세부사업-세부기술간 기술 및 산출물 간 연계 전략                | 136 |

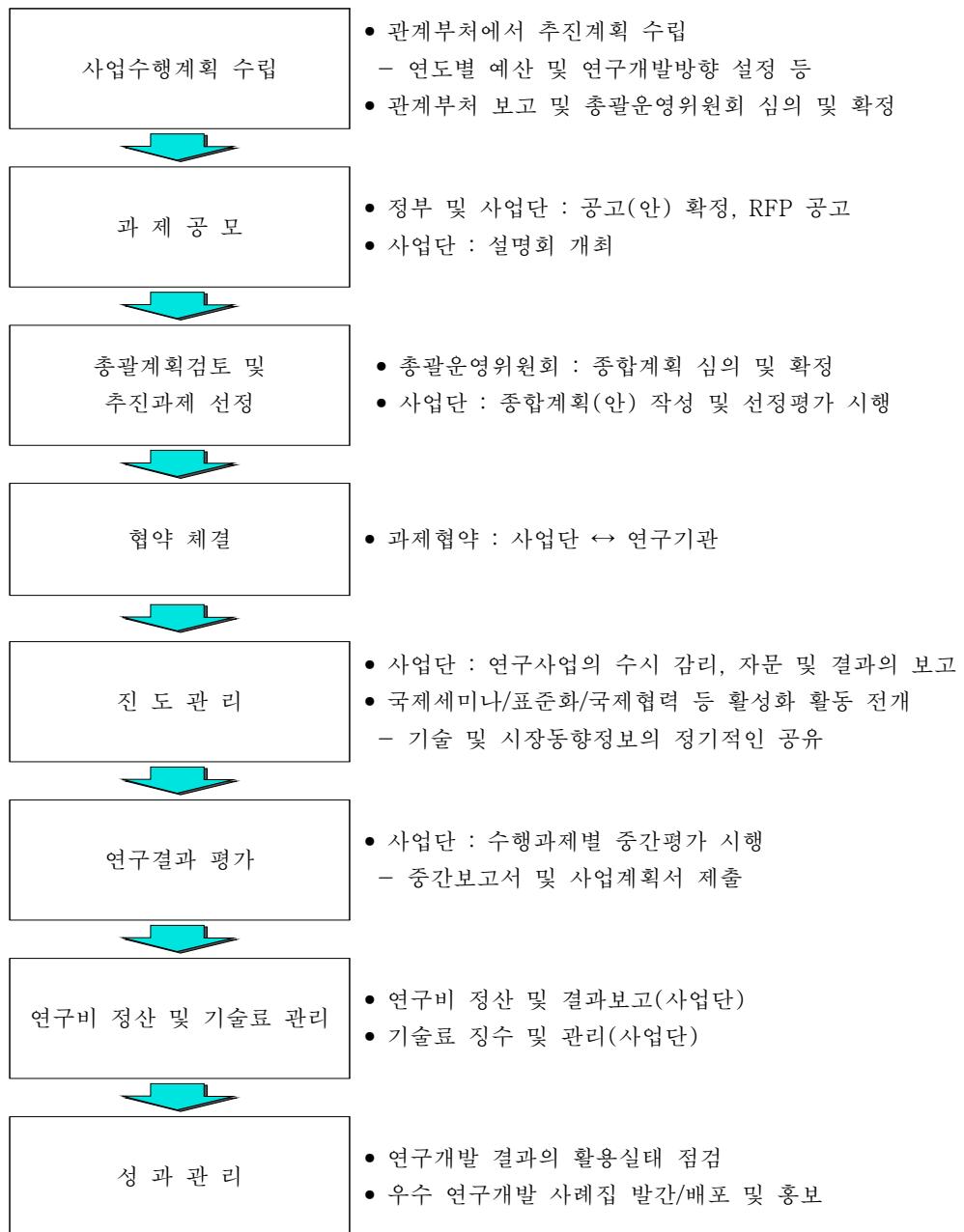

| <그림 111> 사업 추진체계                                    | 146 |

| <그림 112> 사업수행 흐름도                                   | 150 |

| <그림 113> 시스템반도체 및 장비산업 육성전략 개요                      | 152 |

| <그림 114> 제3차 과학기술기본계획 비전 및 목표                       | 153 |

| <그림 115> 제4차 나노기술종합발전계획의 비전 및 목표                    | 155 |

# 1. 추진배경 및 필요성

## 1.1 개념 및 특성

- (지능형 반도체의 개념) 지능형 반도체는 인공지능 시스템을 효율적으로 구현하기 위해 필요한 반도체를 칭함

- 인공지능 시스템이란 인간의 신경계를 모사하여 기억과 학습이 가능한 인공신경망이 구현된 시스템을 의미함

- 현재의 인공지능은 인간 뇌의 기능을 소프트웨어로 모사한 인공신경망을 범용 반도체로 구성된 컴퓨터에서 구동하고 있음

- ※ 범용 반도체: CPU, GPU, DRAM 등 일반적 연산을 위해 사용되는 반도체

- 인공신경망 소프트웨어 알고리즘은 대량의 데이터에 대한 단순한 계산이 특징이므로, 연산기수가 적고 데이터 전송속도가 낮으며 전력소모가 많은 범용 반도체로는 인공신경망 알고리즘을 수행하는 것이 비효율적

- 따라서, 인공신경망 소프트웨어 알고리즘을 보다 효율적으로 처리할 수 있도록 대규모 병렬 연산과 저전력 소모가 가능한 소프트웨어 기반 인공신경망 전용 반도체의 개발이 요구됨

- ※ 소프트웨어 기반 인공신경망 전용 반도체: NPU (Neural Processing Unit), TPU (Tensor Processing Unit) 등 대규모 병렬 컴퓨팅과 저전력 연산 등을 특징으로 하는 반도체

- 궁극적으로는 인공신경망을 소프트웨어가 아닌 직접 하드웨어로 구현하는 새로운 패러다임의 하드웨어 기반 인공신경망 전용 반도체 개발이 필요함

- 이를 위해서는 뇌의 단위 신경세포 기능을 물리적으로 모사하는 신경세포 모방소자의 개발이 선행되어야 함

- 이러한 반도체는 인공지능 시스템을 초저가격, 빠른 학습시간, 초저전력 소비 등의 특성을 갖게 하고, 이는 인공지능 서비스의 개인화를 가능케 할 것임

- ※ 신경세포 모방소자: 뇌의 생물학적 단위 신경세포인 뉴런과 시냅스의 기능을 물리적/전기적으로 모사하는 반도체 소자

- (4차 산업혁명 시대와 인공지능 기술의 중요성) 제 4차 산업혁명의 핵심기술인 인공지능은 산업, 사회, 경제, 문화 등 다양한 분야에 응용될 것으로 전망

- 제 4차 산업혁명은 인공지능, 로봇공학, 사물인터넷, 무인운송수단, 3차원 인쇄, 나노기술과 같은 6대 분야를 포함하며, 단순한 기술의 발전을 넘어서 현재 전 세계 모든 산업 구조에 변화를 가져와 사회경제적, 지정학적, 인구학적으로 단절되었던 모든 분야에 대한 경계를 허물고 융합적인 트렌드의 플랫폼으로서 영향력을 강화해 나갈 것임

- 특히, 6대 기술 중 가장 핵심인 분야는 인공지능으로 그 중심에는 반도체와 소프트웨어가 있으며, 인공지능 기술의 발전에 따라 제품의 혁신, 생산공정 혁신, 새로운 서비스 창출 등 응용 분야가 폭발적으로 증가할 전망

- 인공지능 기술의 발전은 제조업/서비스업을 막론한 전 산업 분야에 고도화된 인간의 전문적 지식과 판단을 뛰어 넘는 지능화를 촉진하여 사회혁신을 가져올 것으로 예상

- (인공지능 기술의 발전) 현재까지 컴퓨팅은 인간이 만든 알고리즘에 따라 정형적이고 반복적인 일에 한정되어 활용되어 왔지만, 인공지능 기술의 발전과 더불어 인간 고유의 영역이라 여겨졌던 학습, 인식, 추론 등이 가능하게 됨

- 최근 인공지능 기술의 발전은 학습에 필요한 막대한 데이터의 확보 및 반도체 기술의 발전에 의한 계산능력의 획기적 개선에 힘입음

- 빅데이터를 활용해 컴퓨터 스스로 패턴을 인식하고 해결방법을 찾아가는 기계학습 방법론들이 도입됨으로 인공지능의 유연성과 적용성이 크게 높아졌고 적용할 수 있는 분야가 확대되고 있음

- 학습 및 인식, 추론 등이 가능하다는 점에서 질병 진단, 금융 관련 투자 및 신용평가 등 산업 예의 적용뿐만 아니라 문화, 예술 등 인간이 수행할 수 있는 거의 모든 분야의 활동에서 인공지능 기술이 활용 가능할 것으로 예상됨

- (사회혁신 가속 반도체 기술) 지능형 반도체는 사회 서비스의 혁신을 가져올 것으로 전망

- 4차 산업혁명에서의 서비스 혁신은 교통, 도시, 국방, 흄, 의료, 교육, 금융, 관광, 제조, 에너지, 농축수산 등 사회 전반에서 동시다발적으로 발생하는 지능정보 서비스의 혁신을 지칭

<그림 1> 4차 산업혁명 혁신 서비스와 지능형 반도체 및 소프트웨어

- 서비스의 혁신은 ICT 시스템, 즉, IoT, UHD, 통신, 클라우드, 빅데이터, 보안, SW플랫폼, 디바이스, 콘텐츠 등의 시스템 구현 혁신으로부터 시작되며 모든 시스템과 서비스의 지능화가 시스템 혁신의 핵심 개념이며, 이의 효율적 구현을 위한 반도체와 소프트웨어 기술 개발이 절대적으로 필요

- 인공지능 시스템은 자동차, 의료기기, 산업기기 등으로 응용 분야를 확장해 갈 것으로 예상되며<sup>1)</sup>, 자율주행, 드론, VR/AR과 같은 미래 서비스의 대중화를 이루는 근간이 될 것임<sup>2)</sup>

- 인간의 두뇌를 모방하여 병렬처리가 가능한 컴퓨팅 아키텍처의 필요성이 커지고 있으며, 지능형 반도체의 고성능화·저전력화와 더불어 뇌모방형 프로세서 기술이 경쟁할 것으로 전망됨

- (지능형 반도체의 구현 목표) 지능형 반도체는 센싱, 인지, 사고·추론, 반응, 저장 등의 기능을 반도체로 구현한 것을 말하며, 인간두뇌 수준의 전력소모로 인간두뇌 이상의 우수한 지능을 구현하는 것이 궁극적인 목표

- 상황정보 또는 환경정보를 입력받는 센싱, 입력된 정보에서 사물과 물체를 구별하는 인지, 응용 및 서비스에 최적화된 사고 및 추론, 행동 및 동작을 구현하는 반응 기능을 인간보다 우수한 성능으로 구현하는 것

<그림 2> 지능형 반도체의 개념과 응용 분야

- 지능형 반도체는 인공지능의 개인서비스를 위한 디바이스(모바일 기기, 지능형 스마트폰 등), 자율이동체(자율주행 자동차, 자율이동형 드론, 물품 수송), 서버형 딥러닝 가속기, 지능형 헬스케어(인공지능 의사, 원격 진료, 웨어러블 헬스케어 기기), 군용장비(무인비행체, 탐지형 로봇), 사회 서비스(금융·예측서비스, 범죄 감시) 등 사회, 경제 전 분야에 응용

1) 출처: Semiconductor Engineering, 2016

2) NVIDIA의 Jenson Wang의 연설, 2016

## 1.2 기술개요

### □ 인공지능 기술 개발 개요

<그림 3> 인공지능 기술개발 역사와 지능형 반도체

- 인공지능 기술은 영국의 Alan Turing이 1950년대에 튜링 테스트 (이미테이션 게임이라고도 부름)의 개념을 제시한 이후 요구되는 컴퓨팅 성능이 매우 크다는 것을 발견한 이후 장기간의 침체기를 겪어왔음

- 다층신경회로망(MLP; Multi-Layer Perceptron) 개념의 도입, 신경망 회로(Neural Net)의 개념이 도입되면서 인공지능 기술의 응용 분야가 다양화되기 시작하였으며, 반도체 기술의 발전과 더불어 소형 컴퓨터에서도 사용가능한(Available) 컴퓨팅 성능이 급격히 증가하면서 각광을 받게 됨

<그림 4> Alan Turing

- 영상인식 분야의 저명한 학회에서 열리는 영상인식 알고리즘 대회인 ImageNet에서 Alex Krizhevsky와 Hinton 교수가 개발한 "두 개의 GPU에서 구현한 신경망 회로인 AlexNet"이 인식률에서 1등을 거머쥐면서 인공지능의 새로운 도약기 마련

- 기계학습(Machine Learning)은 기계가 일일이 명시하지 않은 동작을 데이터로부터 학습하여 실행할 수 있도록 하는 알고리즘이며 결정 트리 학습, 연관 규칙 학습, 서포트 벡터 머신(SVM, Support Vector Machine), 인공신경망 등의 다양한 학습방법이 존재

- 2011년 이후 수 많은 신경망 회로와 이의 다양한 응용분야가 개발되었으며, 다수의 레이어로 구성된 네트워크 구조로 되어 있어 이를 레이어가 많은 넷에서 학습한다고 하여 딥러닝(DL, Deep Learning)이라고 부르게 됨

- 딥러닝은 기계학습의 한 방법으로서 비선형 변환기법의 조합을 통해 높은 수준의 추상화를 시도하는 알고리즘의 집합으로 인공신경망(ANN, Artificial Neural Network)을 기반으로 설계되며, 신경망의 계층이 2개 이상일 경우 심층신경망(DNN, Deep Neural Network)이라 칭함

- 합성곱 신경망(CNN, Convolutional Neural Network), 순환 신경망 (RNN, Recurrent Neural Network), 심층 Q-네트워크 (Deep Q-network) 등의 기술이 최근 많은 관심을 받고 다양한 연구 개발이 진행 중

- 그러나 딥러닝 기반의 인공지능은 현재 가장 빠른 모바일 프로세서보다 1,000배 이상의 성능을 요구하며, 이를 구현하기 위하여 현재 제공되는 인공지능 음성비서 서비스의 전력 소모량 역시 수 kW 이상의 전력을 소모

<그림 5> 인공지능 서비스가 요구하는 성능 및 전력 소모량

- (소프트웨어 기반 인공신경망 전용 반도체) 인공신경망 모사 소프트웨어를 보다 효율적으로 처리할 수 있도록 대규모 병렬 컴퓨팅과 저전력 연산이 가능한 인공지능 전용 반도체

- 현재는 인공신경망을 소프트웨어를 통해 구현하고 이를 기존 중앙연산장치(CPU)와 그래픽 처리장치(GPU)와 같은 범용 반도체를 사용한 컴퓨터를 이용하여 연산하는 것이 대세이나 독립적인 처리·기억장치 인터페이스를 가짐으로써 나타나는 병목현상에 의해 큰 전력소모, 저속 동작이라는 한계를 보이기 시작하면서 학습을 효율적으로 진행하기 위한 ‘특수한 목적을 가진 전용 지능형 반도체인 NPU, TPU가 2015년부터 등장

- 전용 지능형 반도체는 현재 양산되는 메모리를 사용하거나 데이터 전송 대역폭을 넓힌 메모리가 사용되고, 특히 현재 메모리에 연산기를 집적하는 형태가 사용될 것으로 예상됨

- 인공지능 가속 반도체, 초병렬 프로세서를 사용하여 programmability를 최대화하고 다양한 인공지능 알고리즘의 통합적인 병렬 구현이 가능한 기술임

- 초고성능의 병렬 프로세서 시장 안정화 및 차세대 메모리 기술의 출현에 따른 프로세서와 메모리 통합 거대 병렬 컴퓨팅 시장이 성장하고 있으며, 메모리 내부 및 인근에 연산을 포함한 로직을 추가하여 데이터 처리 대역폭 및 에너지 효율을 획기적으로 향상시키는 기술인 PIM(Processing In Memory)에 대한 연구가 활발히 진행

- 인공지능 알고리즘 중 최근 각광받고 있는 딥러닝 알고리즘을 구현하는 DNN은 외부 메모리로부터 대량의 시냅스 데이터를 읽어 인지정보 처리를 수행하는 데이터 집약적인 특성을 가지므로 메모리 대역폭을 감소시키기 위한 기술이 매우 중요

- (하드웨어 기반 인공신경망 전용 반도체) 인공신경망을 소프트웨어가 아닌 직접 하드웨어로 구현하는 새로운 패러다임의 반도체

- 소프트웨어 기반의 인공지능 시스템은 뇌의 시냅스와 뉴런의 기능을 수식적으로 정의하고 코딩하여 기존 폰노이만 구조의 컴퓨터를 통해 연산하기 때문에 전용 지능형 반도체를 채용한다 하더라도 궁극적으로는 컴퓨터 가격, 학습시간, 소비전력 면에서 한계를 보일 것임

- 이러한 한계를 해결하기 위해, 뇌의 시냅스와 뉴런의 기능을 모방한 하드웨어 기반 인공지능 시스템 기술이 부각됨

- 이는 뉴런과 시냅스의 기능을 수학적 연산이 아니라 신경세포 모방소자의 물리적 특성으로 모사하기 때문에, 잡음이 있고 변화하는 환경에서 빠른 학습시간과 적은 에너지 소모로 높은 효율의 성능을 보여줌

<그림 6> 하드웨어 기반 인공지능 시스템

- 인간의 뇌는 1,000억개의 뉴런과 100조개 이상의 시냅스가 존재함. 따라서 뇌-모방 (Brain-like) 형태인 인공지능 시스템을 구현하기 위해서는 뉴런/시냅스를 고집적도로 구현하는 것이 매우 중요함. 따라서 실제 두뇌의 뉴런/시냅스 용량 수준으로 모사가 가능한 새로운 반도체 소자(신경세포 모방소자)의 개발이 하드웨어 인공지능 시스템 분야에서 필수적임

- 인공지능 하드웨어의 기본 구성요소인 뉴런과 시냅스에 기존의 수학적 연산을 위한 소자와 회로를 벗어나, 스파이킹 인공 신경망(SNN, Spiking Neural Network) 기반의 새로운 개념이 도입되고, 시스템 설계에서도 새로운 아키텍처와 구현 방식에 기반을 두고 있어 컴퓨팅 기술에 패러다임 변화가 일어날 것으로 예상

- 생물학적 시냅스를 모방하는 소자에 기존 메모리를 창의적으로 변형하여 사용하거나 새로운 형태의 메모리 소자가 필요하고, 뉴런모방 소자/회로와 아키텍처, 그리고 알고리즘이 하나의 시스템으로 융합하는 형태로 발전

- 현재의 기술은 CMOS 기반의 SRAM, floating gate을 시냅스로 활용하는 신경 세포 모방 회로 기술과 멤리스터, 스핀트로닉스 등의 이미징 소자를 뉴런 또는 시냅스로 사용하는 신경 세포 모방 소자 기술로 구분 할 수 있음

- (지능형 반도체 기술의 최종 목표) 가격, 성능, 전력문제를 동시에 해결하기 위한 반도체 기술을 개발하여 “모든 ICT 기기에 인공지능을 부여하는” 사회로의 발전을 위한 기반적인 기술을 실현하는 것

- 4차 산업혁명에서의 핵심기술은 지능형 반도체와 인공지능 소프트웨어이며, 이는 사회 전반에 걸쳐서 정보기기화 혁명(IDX, Intelligent Digital Transformation)이 발생한다는 것을 의미함

- 현재의 인공지능 서비스는 빅데이터 서버와 서비스 클라이언트가 상호 연결된 서비스로서, 예를 들어 음성비서 서비스를 한번 사용할 때마다 작은 배터리 한개 만큼의 에너지가 지속적으로 사용되는 상황이 발생

- 서버-클라이언트 수준의 인공지능 서비스를 넘어서 작은 반도체에 완전한 인공지능을 구현할 수 있는 기술을 개발해야만 진정한 인공지능 기반의 4차 산업혁명에 의한 사회 구현 가능

### 1.3 기술개발 필요성

- (인공지능 서비스의 대중화) 이를 위해서는 현재의 모바일 AP보다 1,000배 이상의 고성능을 가지면서 전력소모량은 획기적으로 줄이는 기술 개발이 필요

- 현재의 반도체 기술은 스케일링 한계점에 도달하여 이를 극복하기 위한 기술 혁신이 필요

- 4차 산업혁명의 대두와 더불어 초고성능 컴퓨팅을 요구하는 서비스가 등장하고 있어서 인공지능을 위한 새로운 컴퓨팅 패러다임의 변화가 필요

- 빅데이터 처리, 분석을 기반으로 효율적인 판단을 내리는 인공지능 기술에 최적화된 새로운 구조의 컴퓨터 구조의 개발 필요성이 점차 커지고 있음

- 기존 폰 노이만(von Neumann) 구조 기반 고성능 연산 능력 향상에서 탈피하여 데이터의 저장과 분석을 기반으로 효율적인 판단을 내리는 인공지능 기술에 최적화된 새로운 컴퓨터 구조 개발의 필요성이 증대되고 있음

- 폰 노이만 구조는 산술연산 장치와 저장 장치가 분리되어 있어, 연산을 담당하는 프로세서의 고성능화에도 불구하고 산술연산 장치와 저장 장치 간의 병목 현상으로 인해, 인공지능과 빅데이터에 사용되는 기하급수적인 데이터의 증가에 제대로 대처하지 못하고 있음

- 실제 시스템에서 인공 신경망을 수행하기 위해서는 알고리즘의 정확도 손상 없이 계산량을 최소화하는 최적화가 필수적이며, 이는 고성능을 유지하면서 서버의 전력 소비량을 감소시키는 역할을 함

- 인공신경망 전용 반도체는 신경 구조와 유사한 구조를 가진 하드웨어를 의미하며, 병렬처리를 이용해 ‘학습’ 동작을 수행하여 기존의 구조보다 훨씬 빠른 데이터 처리할 수 있음

- (하드웨어 기반의 인공지능 시스템) 4차 산업혁명 시대의 인공지능 시스템은 현재의 “범용 반도체를 사용한 고성능 빅데이터 서버 인공지능 컴퓨팅”에서 “인공지능 시스템 전용 반도체를 채용한 아키텍처”를 거쳐 “신경세포 모방 소자를 사용한 하드웨어 기반 인공지능 시스템”으로 발전 전망

- 현재의 지능형 반도체 기술은 도입기에 속하며 인공신경망을 소프트웨어로 구현한 서버 프로세서 기반의 인공지능 서버와 클라이언트로 구현되어 AI 음성비서 등의 상용 서비스를 구현하여 서비스 중

- 인공지능 기술의 혁신기와 더불어 자율주행차, 인더스트리 4.0(생산체계 혁신), 휴머노이드, 인공지능 개인형 디바이스, AR/VR 등의 서비스를 제공하는 모든 ICT 디바이스에 인공지능 컴퓨팅 환경을 구현하기 위한 인공지능 시스템 전용 반도체 개발이 필요함

- 국내외 글로벌 기업과 연구소에서 다양한 형태의 인공지능 시스템 아키텍처 개발이 이루어질 것이나, ICT 디바이스 별로 요구하는 다양한 형태의 컴퓨팅 요구 성능에 최적화된 전용 반도체와 소프트웨어가 개발될 것임

<그림 7> 지능형 반도체의 현재와 미래 혁신 방향

- 신사회 지능형 반도체 기술을 주도하기 위한 원천 기술은 지능형 반도체 설계기술, 소자공정 기술 등이며, 4차 산업혁명 대응을 위하여 이를 위한 적극적인 기술 개발이 필요

- 도약기에는 매니코어 프로세서, 신소자 기술, 신소자 공정 기술 분야에서 핵심 원천기술이 개발되고, 변혁기에는 이를 기반으로 한 병렬 컴퓨팅 AI 프로세서가 서비스됨과 동시에 이를 융합한 뉴메모리 융합 프로세서, 패키징/원자단위공정 기술이 개발되고, 신사회에 이를 기반으로 한 두뇌기능모사 AI 컴퓨터가 본격 서비스 될 예정

- 뇌와 같이 복잡하고 집적도가 높은 구조의 하드웨어 기반 인공지능 시스템 개발을 위해선 신경동작 메커니즘에 대한 기초연구에 근거한 시냅스/뉴런을 모사한 소자/소재 개발 및 시냅스/뉴런 소자를 적용한 지능형 집적회로에 대한 종합적인 융합연구가 필요함. 뿐만 아니라, 하드웨어 기반 인공지능 시스템은 컴퓨팅 패러다임을 바꿀 수 있는 혁신 기술로서 난이도가 높기 때문에 기업과 정부의 지속적인 투자가 필요

- (인공지능용 하드웨어 플랫폼) 인공지능을 실현하기 위한 하드웨어 플랫폼의 확보가 절대 우선으로 중요하며, 다양한 응용 분야에서 원활한 인공지능 기술 적용을 위해 고성능 저전력 하드웨어 플랫폼의 개발이 필요

- 퀄컴, IBM, NVIDIA, CEVA 등 인공지능 분야의 선두 업체에서는 다양한 플랫폼 기술을 개발

하여 다양한 분야에 활용하기 위한 응용 플랫폼 구축에 집중하고 있는 상황이며, 한국의 반도체 분야 경쟁력을 지속적으로 유지하기 위해서는 최신의 지능형 반도체 기술 개발이 절대적으로 필요한 상황임

- 퀼컴은 “Zeroth”라는 뇌·모방 컴퓨팅 플랫폼을 이용하여 모바일 환경에서 딥러닝을 사용할 수 있게 하여 이를 통해 영상, 음성 인식 응용 프로그램을 개발할 수 있으며, 이는 신경 처리 장치라고 불리는 인공지능 가속기 칩과 이를 사용하기 위한 소프트웨어 플랫폼으로 이루어져 있음

- IBM의 “TrueNorth”는 뇌를 모방한 뉴런과 시냅스에 해당하는 부분으로 구성되어 있기 때문에 70mW 초저전력으로 동작할 수 있으며 모바일 기기나 센서에 임베디드 되어 시각, 청각, 복합감각과 같은 인지 어플리케이션에 사용될 수 있음

- NVIDIA DRIVETM PX2는 자율주행 차량의 생산을 가속화 할 수 있도록 지원하는 개방형 자동차 AI 플랫폼으로, LiDAR<sup>3)</sup>, RADAR, 초음파 센서는 물론 여러 대의 카메라를 통해 데이터를 수신, 병합할 수 있는 융합기술을 통해 자동차 주변의 정적, 동적 물체에 대한 데이터를 만들 수 있음

- CEVA는 저전력 임베디드 시스템에 딥 러닝 기능을 제공하는 DSP 기반 제품을 선보이고 있는데, 임베디드 시스템에서 3D 비전, 컴퓨터 활용 사진 기술, 시각적 인지 및 분석 등의 작업을 수행

□ (반도체 기반 신경세포 모방소자) 인공지능 시스템의 하드웨어적 구현을 위해서는 고에너지 효율 반도체 소자, 차세대 메모리, 재구성 가능 논리 회로, 삼차원 집적 구조, 초병렬 컴퓨팅 구조, 인간 뇌의 시냅스와 뉴런을 반도체 기술로 구현한 신경세포 모방소자 기술 개발이 필요

- 인간의 뇌는 1,000억개의 뉴런과 뉴런 당 100조개 정도의 시냅스가 존재하므로 이를 반도체 기술로 모사하기 위해서는 뇌의 집적도, 에너지 효율, 삼차원 구조, 정보처리 메커니즘을 모방해야 하나, 이러한 요구 조건을 만족하는 반도체 소자가 아직까지 개발되지 않고 있어 기술적 돌파구가 절실한 상황

- 지능형 반도체 기술의 원천기술 및 경쟁력 확보를 위해서는 기존의 소프트웨어 기반의 방법에서 벗어나 하드웨어 기반의 원천 반도체 소자 기술을 확보하고 인간 뇌세포를 모사하는 초병렬 고속연산을 구현하는 신경세포 모방 반도체 기술의 확보가 필수적임

- 미국과 유럽은 2008년부터 SyNAPSE (Systems of Neuromorphic Adaptive Plastic Scalable Electronics), FET (Future and Emerging Technologies of the EU)를 중심으로 두뇌의 구조와 동작을 모방한 지능형 반도체의 원천기술 연구를 진행하고 있음

- 중국도 2014년부터 기업 중심으로 인공지능센터 설립과 미국/유럽의 인재를 스카웃하여 원천기술을 개발하고 있음

- 반면 한국은 일부 대학중심의 소규모 연구가 진행되고 있으나 초기적인 성과에 머무르고 있는 상황이므로 정부와 기업의 지원이 절실한 상황임

□ (3차원 집적화 기술의 적용) 초고성능의 지능형 컴퓨팅과 고도의 데이터 대역폭을 가지는 고속

---

3) Light detection and ranging

메모리를 병목현상 없이 집적하기 위해서는 고도의 3차원 집적(3D Integration)기술 개발이 필요

- 기존의 반도체 시장 성장의 주된 엔진은 트랜지스터의 소형화 기술, 즉 2차원 scaling 기술의 발전이 핵심으로 작용하였음. 그러나 트랜지스터의 크기가 극단적으로 작아지면서 이들 간의 연결이 전체 성능 향상을 제한하게 되었으며, 이를 극복하기 위하여 3차원 집적 기술이 연구 개발되고 있음

- 3차원 집적화 기술은 3차원 웨이퍼 레벨 패키징, 2.5/3차원 인터포저 기반 집적, 3차원 스택 IC(3D-SIC), 모노리식 3차원 IC, 3차원 이종 집적, 3차원 시스템 집적 등 다양한 기술을 포함하고 있음. 기존에는 상대적으로 큰 사이즈를 갖는 TSV(Through Silicon Via)를 이용하여 다이를 적층하거나 인터포저를 사용하여 다이를 연결하는 등의 방식에서, 점차 통합된 한 번의 공정을 통해 via 수준의 고밀도로 층간 연결이 가능한 모노리식 3차원 집적 기술이 개발되고 있음

- Xilinx는 2013년 28nm 공정을 사용한 FPGA와, 65nm 공정으로 제작된 실리콘 인터포저, 마이크로 범프 기술에 기반한 3D IC 기술을 사용하여 다이 사이의 대역폭과 단위 전력당 대역폭 모두를 향상시킨 최초의 3D FPGA인 UltraScale을 발표하였음

- 삼성은 3차원 원통형 CTF(Charge Trap Flash) 셀 기술과 3차원 수직적층 공정 기술을 개발함으로써, 2013년에 세계 최초로 3차원 수직 구조의 NAND 플래시 메모리 양산을 시작하였으며, 이후 메모리 분야에서의 모노리식 3차원 집적 기술을 선도하고 있음. 그러나 컴퓨팅 (로직) 반도체 분야에서는 두각을 드러내지 못하고 있음

- CEA-Leti는 SOI(Silicon-On-Insulator) 기반의 상부 실리콘막을 선택적으로 전사하여 둘째 층으로 사용하는 기술을 바탕으로 모노리식 3차원 집적 기술을 선도하고 있으며, 2015년에는 하부 층에 텅스텐 배선 이후 SOI 기판을 본딩하고 지지기판을 제거하여 실리콘막을 남긴 후 상부 공정을 계속해서 진행하는 CoolCube™ 기술을 공개하였음

- 3차원 집적화 기술은 공정 자체의 개발뿐만 아니라 열 방출, 설계 방법론 및 소프트웨어 지원, 불량 평가, 표준화 등 다양한 문제들을 해결해야 하며, 이를 위해 메모리 통합/이미지 센서 통합, 이종 반도체 3차원 집적, 확장형 반도체 집적, 모노리식 3차원 집적, 저전력/저발열/열방출 고려 설계 기술 개발이 절실함

□ (신산업을 발판으로 한 국내 반도체 산업의 재도약) 4차 산업혁명의 핵심기술인 지능형 반도체에 집중 투자를 통하여 국내 반도체 산업의 재도약을 도모하며, 핵심기술 개발을 통하여 반도체 전후방 산업의 동반 성장

- 지난 수십 년간 반도체 산업의 발전을 지배해 왔던 '무어의 법칙'은 반도체 제작 공정의 스케일링을 지속적으로 가능하게 해 왔으나, 7nm 수준에서 물리적 한계에 부딪히며 발전이 정체된 상황

- 국내의 경우 메모리 반도체 기술의 발전이 강하게 이루어지면서 국내 반도체 산업 성장의 견인차 역할을 해 왔고, 국내 수출의 상당부분을 차지하고 있지만 현재의 호황이 지속되리라는 보장을 누구도 하지 못하고 있음

- 반면, 4차 산업혁명으로 촉발된 인공지능 기술의 대중화를 위해서는 현재의 모바일 AP보다

1,000배 이상의 고성능을 가지면서 전력소모량은 획기적으로 줄이는 기술 개발이 필요하나, 현재의 CMOS 반도체는 스케일링의 한계점에 다가가고 있어 이를 극복하기 위한 기술 혁신이 필요한 시점

- 국내에서 강점을 가지고 있는 메모리 반도체 기술 역시 지능형 반도체를 위해서는 현재의 메모리 대역폭 보다 100배 이상의 대역폭을 구현한 새로운 형태의 메모리 기술이 필요한 시점에 있음

- 지능형 반도체는 현재의 반도체의 시장 성장 한계를 극복하고, 국내 반도체 산업의 재도약을 위한 신산업을 위한 신기술로서 전반적인 전후방 산업 활성화 기술

- 4차 산업혁명을 필두로 하는 신서비스를 사회 보편적으로 확산하기 위하여 지능형 반도체의 개발을 통하여 모든 디바이스에 인공지능 컴퓨팅 기능을 부여함으로써 사회전반적인 산업혁명

- 지능형 반도체는 지능정보 컴퓨팅의 요구 성능별로 적합한 구조의 반도체 개발이 가능하므로 서비스의 특성, 요구 성능, 전력소모량의 다양성에 따라서 수많은 종류의 지능형 반도체 개발이 가능함

- 지능형 반도체는 아키텍처, 반도체 설계, 반도체 회로, 제조 공정 등 반도체 산업 전 분야에서의 혁신을 이끄는 사업으로서 국내 반도체 산업의 재도약을 도모

<그림 8> 4차 산업혁명 서비스를 기반으로 하는 지능형 반도체의 기술혁신 및 산업도약

## 2. 4차 산업혁명시대의 특징 및 주요국 분석

### 2.1 개요 및 특성

- (4차 산업혁명의 개요) 우리 사회는 1,2차 산업혁명을 거쳐 현재 3차 산업혁명시대를 살고 있으며 4차 산업 혁명의 도래를 목전에 두고 있음

- 18세기 중반 증기기관의 등장으로 비롯된 산업의 기계화가 초래한 1차 산업혁명에 이어, 전기 에너지의 도입에 따른 대량생산 체제 구축과 이에 의한 2차 산업혁명을 경험한 바 있음

- 현재 우리는 반도체 및 컴퓨터의 발명과 확산을 통한 ICT 산업의 형성과 정보화 사회로 진입하는 등, 우리 사회가 디지털 정보체제로 전환함에 따른 3차 산업혁명의 시대를 살고 있음

- 디지털 세계의 급격한 확산과 데이터의 대량 생산과 유통은 실제 세계와 가상공간의 경계의 구분을 모호하게 하는 새로운 융합의 세계로 우리를 유도하고 있으며, 2016년 1월 다보스 포럼에서는 이 같은 사회현상을 제 4차 산업혁명의 시작점이 될 것으로 전망한 바 있음

- 이에 따라 미래학 전문가 및 관련 주요 연구기관들은 제 4차 산업혁명과 미래사회의 전망들을 활발히 논의하기 시작했으며 독일, 미국 등 주요 국가들도 도래할 미래사회를 선도하기 위한 국가차원의 전략과 정책 수립을 추진 중에 있고 우리나라도 정부 및 민간영역에서 다양한 대응방안을 수립 중에 있음

- (4차 산업혁명의 핵심 특징) 4차 산업혁명은 초연결성과 초지능화의 두 가지 핵심 요소의 융합화를 기반으로 ‘모든 것이 상호 연결되면서 동시에 보다 지능화된 사회’를 특징으로 하는 사회로 전환 시킬 것으로 전망

- 초연결사회로의 진입

- 사물인터넷 (IoT), 클라우드 등 ICT 산업의 발전은 인간과 인간, 인간과 사물, 사물과 사물의 연결성을 급격하게 확장시키고 있는 등, 이미 우리사회는 초연결사회의 초기단계를 지나고 있음

- 이에 따라 인터넷과 연결된 사물의 수가 2015년 182억개에서 2020년 약 500억개로 증가하면서 이에 따른 시장규모도 2015년 5조2000억원에서 2020년 16조 5000억원에 이를 전망이며, 2020년까지 인터넷 가입자 30억명, 500억개의 디바이스가 상호 연결되는 초연결 네트워크를 형성 할 것으로 예측

- 초지능화 사회로 전환

- 인공지능과 빅데이터의 연계 및 융합으로 기술, 산업구조, 및 사회가 초지능화로 전환

- 2016년 3월 인간 이세돌과 인공지능 컴퓨터 알파고와의 바둑 대결로 인공지능이 우리 생활 속이 이미 침투하고 있음을 각성하는 계기가 됨

- ※ 2017년 한국과학기술단체총연합회에서 과학기술인을 대상으로 실시한 ‘4차 산업혁명에 대한 인식조사’에서 응답자 2,350명 가운데 89%가 ‘현재 4차 산업혁명이 진행되고 있다’라고 답변

- IBM 인공지능 컴퓨터인 왓슨의 의료기기 진출 등 산업분야에서는 이미 딥 러닝과 같은 기계학습에 의한 산업기술들이 적용되기 시작

- 이 같은 추세에 맞추어 트랙티카 보고서에 의하면 인공지능 산업시장은 2015년 2억 달러 시장에서 2024년에는 약 111억 달러로 급성장 할 것으로 전망 (Tractica, 2015) 할 뿐 아니라, 인공지능이 탑재된 스마트 머신의 시장규모는 2024년 412억 달러에 이를 것으로 예측 (BCC Research, 2014)

- 보다 신속하고 광범위한 혁명의 전개

- 과거 1~3차 산업혁명의 발아와 전개는 오랜 기간이 소요되었으나, 4차 산업혁명은 이들을 떠받치고 있는 주요 기술 즉, 반도체, ICT, 컴퓨터/SW 등의 핵심 기술들이 클라우드, IoT, 빅데이터, 네트워크, 및 초고속 통신기술과의 결합이 용이하여 이에 따라 보다 신속한 적용과 폭넓은 확산이 전개 될 것으로 기대됨

□ (4차 산업혁명에 의한 미래사회 변화) 4차 산업혁명은 산업구조, 사회, 및 문화 등 생활전반의 근본적인 변혁을 초래 할 것으로 전망

- 기술·산업 구조적 측면

- 초연결성과 초지능화의 실현은 CPS (Cyber Physical System) 기반의 스마트 팩토리 (Smart Factory)의 출현 등 새로운 스마트 비즈니스 모델을 창출할 것으로 기대됨

- 특히 제조업 분야에서는 인간의 노동력을 대체하는 수단이 등장함에 따른 리쇼어링 등 벌써부터 산업 생태계의 변화조짐마저 나타나고 있으며 독일의 경우, 2011년부터 제조업 혁신을 위한 인더스트리 4.0 (Industry 4.) 정책을 수립하여 추진하고 있음

- 이와 함께 사물인터넷 및 클라우드 등 초연결성을 기반한 플랫폼의 발전으로 O2O(Online to Offline) 비즈니스가 등장하는 한편, 공유경제 (Sharing Economy) 및 온디맨드 경제(On Demand Economy)와 같은 새로운 경제형태도 부각하고 있음

- 자동화의 강화로 일자리 감소를 염려하는 전망이 있는 한편, 4차산업혁명과 관련한 인공지능, 3D 프린팅, 빅 데이터, 및 산업로봇 분야에서 약 200만개의 새로운 일자리가 창출되고 그 중 65%가 신생직업이 될 것이라는 전망도 있음(GE, 2016)

- 이에 따라 컴퓨터/IT, STEM(Science, Technology, Engineering, Mathematics) 분야에서의 보다 혁신적이고 다학제적인 창의적 인재양성과 고급 전문 인력 육성 프로그램 개발 또한 요구되고 있음

- 사회 문화적 측면

- 지능정보기술을 기반으로 한 새로운 의사결정 시스템이 도입되면서 개인의 생활, 각종 사회 단체 및 조직의 운영체제 등 사회 문화 전반에 걸쳐 비용감소, 서비스의 고도화, 편의성을 제공함과 함께, 알고리즘 의존적인 체계가 유발할 수 있는 비의도적인 차별성, 편향성, 비윤리성, 편협성 등의 역기능에 대한 사회-윤리적 잇슈가 새롭게 대두 될 것으로 예상

- 빅데이터, 클라우드 등 초연결시대의 도래로 온-오프라인 간의 ‘더 많은 연결’과 ‘더 빠른 연결’은 더욱 가속화 될 것이며 인공지능과 로보틱스, IoT의 융합 등 사물간의 정보통신은 사람의 개입 없이도 작업의 신속하고 효율적 업무수행을 가능케 할 것임.

- 이 같은 다종, 다양한 융합 네트워크의 발전은 사이버공간에 국한되었던 기존의 위협들이 인간이나 사물 등 현실공간으로 전이가 될 위험성이 더욱 높아질 것으로 전망됨에 따라 기존의 정보보호의 패러다임에 근본적인 변혁이 요구됨

- 스스로 판단하고 의사결정을 내리는 인공지능의 적용확산은 필연적으로 인간사회와의 공존을 위한 새로운 규범 (윤리 및 법)을 요청하고 있으며 유럽연합의 경우, 이에 따른 법제화 움직임이 활발히 전개되고 있음

## 2.2 주요국 동향

### □ 미국

- IBM의Watson, GE의 사물인터넷, Google의 인공지능기반 서비스, Tesla의 무인자동차 등 미국의 글로벌 기업은 4차 산업혁명시대의 주도권을 확보하기 위한 기술력 확보에 주력하고 있음

- 미국정부 또한 대표적으로 ‘새로운 미국혁신전략 (New Strategy for American Innovation)’을 기반으로 뇌 이니시어티브 전략, 스마트시티 전략, 첨단자동차 전략, 고성능컴퓨팅 지원전략 등 4차 산업혁명을 선도하고 첨단산업을 성장시키기 위한 국가 차원의 정책을 수립하여 시행하고 있음

<표 1> 새로운 미국혁신전략의 주요 내용

| 주요 전략분야                                | 주요 전략 내용                                                                                   |

|----------------------------------------|--------------------------------------------------------------------------------------------|

| 첨단 제조업<br>(Advanced Manufacturing)     | 기업과 국민들에게 보다 많은 경제적 편익을 가져다 줄 수 있는 첨단 제조업 육성                                               |

| 정밀의학<br>(Precision Medicine)           | 환자 개인별 체질, 건강 상태, 질병 이력에 초점을 맞춘 효과적 치료 수단 개발                                               |

| 두뇌이니셔티브<br>(BRAIN Initiative)          | 인간의 뇌활동 연구를 통해 각종 뇌신경 질환을 효과적으로 진단, 치료함으로써 사회 경제적 부담 해소                                    |

| 스마트시티<br>(Smart Cities)                | 주요 지역 및 도시 간 협력 체제를 통한 스마트시티 구축으로 공동의 도시 문제 해결                                             |

| 첨단자동차<br>(Advanced Vehicles)           | 센싱, 컴퓨팅, 데이터 과학 분야의 획기적 발전으로 차량 간통신과 자율 주행이 가능해짐으로써, 운전자의 실수로 발생하는 차량사고의 90% 이상을 줄일 것으로 기대 |

| 고성능컴퓨팅<br>(New Frontiers in Computing) | 미 정부는 '15년 7월 '국가전략컴퓨팅이니셔티브(NSCI)'를 발표, 고성능컴퓨팅을 활용한 공공 서비스 개선, 경제 성장 기여, 새로운 과학적 발견 기대     |

출처: NIA(2015)

- 브레인 이니셔티브 정책

- 과학기술정책국 (OSTP) 법부처 차원의 브리엔 이니셔티브 정책을 수립하고 10년간 총 30 억 달러의 투자를 진행

- 인간의 뇌지도 작성과 의식, 지각, 행동 등 외 활동의 전 분야에 걸쳐 진행되고 있는데, 이 중에서 기초연구가 80%, 뉴로모픽 칩 (IBM), 뇌 스캔 이미지 분석 (Inscopix), 뇌 시뮬레이션 (Google) 등이 20%비중을 차지

- OSTP에는 DARPA(국방고등연구계획국), FDA(식품의약국), NSF(국립과학재단), NIH(국립보건원)등이 참여하고 있음

## □ 일본

- 장기침체를 극복하고 새로운 성장동력을 발굴하기 위한 일환으로 수립한 '일본재통전략 2016'에서는 4차 산업혁명을 핵심성장 전략으로 설정하고 정부주도의 정책으로 진행

- 일본 정부의 입장은 사물인터넷, 빅데이터, 인공지능, 로봇 등 미래 기술력을 확보하고 이를 바탕으로 최첨단 경제·사회로 전환하겠다는 전략임

<표 2> 제 4차 산업혁명에 대한 일본정부의 7가지 대응방침

| 대응전략 |                                | 세부내용                                                                                                                                                                          |

|------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 데이터 이용·활용·촉진을 위한 환경 정비         | <ul style="list-style-type: none"> <li>• 데이터 플랫폼의 구축, 데이터 유통시장의 창출</li> <li>• 개인 데이터의 이용·활용·촉진</li> <li>• 보안기술이나 인재를 키워내는 생태계의 구조</li> <li>• 제4차 산업혁명의 지적재산 정책의 방향</li> </ul> |

| 2    | 인재육성·인재획득·고용시스템의 유연성 향상        | <ul style="list-style-type: none"> <li>• 새로운 요구에 대응한 교육시스템의 구축</li> <li>• 글로벌 인재의 획득</li> <li>• 노동시장 및 고용제도의 유연성 향상</li> </ul>                                                |

| 3    | 이노베이션·기술개발의 가속화(『Society 5.0』) | <ul style="list-style-type: none"> <li>• 오픈 이노베이션 시스템의 구축</li> <li>• 세계를 주도하는 이노베이션 거점의 정비</li> <li>• 국가사회 실증의 가속 (인공지능 등)</li> <li>• 지적재산관리이나 국제표준화의 전략적 추진</li> </ul>       |

| 4    | 금융조달(파이낸스) 기능의 강화              | <ul style="list-style-type: none"> <li>• 리스크 매니지먼트 공급을 위한 에퀴티 파이낸스의 강화</li> <li>• 제4차 산업혁명을 향한 무형자산투자의 활성화</li> <li>• 펀테크를 중심으로 하는 금융/결재 기능의 고도화</li> </ul>                   |

| 5    | 산업구조·취업망 전환의 원활화               | <ul style="list-style-type: none"> <li>• 신속·과단정 있는 의사결정을 가능케 하는 거버넌스 체제 구축</li> <li>• 신속하고 유연한 사업재생</li> <li>• 사업재생을 가능케 하는 제도 환경 정비</li> </ul>                               |

| 6    | 제4차 산업혁명의 중소기업, 지역경제에 파급       | <ul style="list-style-type: none"> <li>• 중소기업과 지역에 사물인터넷 등의 도입·이용·활용 기반구축</li> </ul>                                                                                          |

| 7    | 제4차 산업혁명을 향한 경제사회 시스템의 고도화     | <ul style="list-style-type: none"> <li>• 제4차 산업혁명에 대응한 규제 개혁의 모습</li> <li>• 데이터를 활용한 행정 서비스의 향상</li> <li>• 전략적인 제휴 등을 통한 글로벌 전개의 강화</li> <li>• 제4차 혁명의 사회 확산</li> </ul>       |

출처: 한국표준협회(2016.11.)

- 일본 정부는 인공지능 기술 및 산업화 분야의 선도적 역할을 위해 'AI 기술 전략회의'를 신설하고 제조, 물류, 의료 등 산업 전 분야에 AI를 전면적으로 적용하기 위한 로드맵을 2016년 11월 발표

- 특히 자국의 기술위위 분야인 로봇산업의 지속적인 경쟁력 유지를 위해 2015년 1월에 발표한 '로봇 신전략'에서는 인공지능을 접목하여 세계 최고수준의 로봇 활용력과 대중화를 지속적으로 선도 해 나가겠다는 전략

## □ 독일

- 자국의 제조업 경쟁력 구축을 목표로 스마트 제조시스템 구현을 위한 ‘인더스트리 4.0’ 전략을 수립

- 스마트공장의 목표는 빅 데이터, AR, 3D 프린팅, 클라우드, 사이버보안, IoT, 시스템통합, 시뮬레이션, 로봇 등 지능형 첨단기술을 통해 제조업의 글로벌 경쟁력을 확보하는 것으로 독일의 SAP, 지멘스, 보쉬 등 글로벌 제조업체들이 참여

- 초기 독일 내 기업 중심으로 전략을 추진하였으나 2015년부터는 정부와 학계가 참여하는 플랫폼 4.0으로 전환하여 민-관 공동 대응방식으로 확대함으로써 실질적으로 정부의 적극적 개입과 주도 방식으로 전환

- 프라운호프연구소를 중심으로 연간 21억 유로의 예산을 투입하여 민간 및 공공분야의 위탁연구를 수행중이며 주요 연구분야로는 보건·환경, 보안·보호, 이동성·교통, 서비스의 생산·공급, 정보통신, 에너지·자원 등 6개 분야임

- 2016년 4월에 발표한 ‘디지털 전략 2025’는 디지털 경제로의 전환을 위한 망 고도화, 창업 활성화, 혁신제도, 스마트 네트워크, 정보보안, 중소기업 사업모델, 인더스트리 4.0, 혁신적 기술개발, 디지털 교육, 디지털 청 등 10대 추진과제로 추진

## □ 중국

- 4차 산업혁명의 혁신기술개발을 과감히 추진함으로써 세계의 생산공장이라는 양적 성장 차원을 벗어나 질적 성장의 결정적 계기로 삼음

- 2015년 5월 중국 정부는 13차 5개년 계획 (2016~2020년)의 일환으로 ‘중국 제조 2025’를 발표하였으며 주요 내용으로는 모든 제조업 분야에서의 혁신역량 제고, 품질제고, IT·제조업과의 융합, 친환경 등 4개 과제를 제시

- 상기의 목표를 실현하기 위한 10대 중점 육성 산업으로 ICT, 로봇, 교통, 소재, 의료분야 등이 포함됨

- 또한 같은 해 모바일 인터넷, 클라우드 컴퓨팅, 빅데이터, IoT 등의 기술과 제조업의 결합, 전자상거래, 핀테크, 산업 인터넷 산업을 활성화를 위한 ‘인터넷플러스’ 정책을 발표

- 특히 2015년 3월 발표한 ‘차이나브레인’에서는 인간과 기기간의 상호작용, 드론, 무인자동차 등 미래 혁신기술 및 서비스를 포함한 산업 전반에 인공지능을 적용할 계획을 제시함

<표 3> 중국의 인공지능 정책 방향

| 구분             | 정책 방향                                                                                                                                                                                    |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 인공지능 신규산업 양성   | <ul style="list-style-type: none"> <li>음성, 동영상, 지도 등의 라이브러리 구축, 인공지능의 기초 자원과 공공 서비스 등 창의적 플랫폼 건설</li> <li>주요 인공지능 기술의 연구와 산업화를 추진</li> <li>인공지능의 스마트 상품, 공업제조 등 영역에서의 상업화를 추진</li> </ul> |

| 주요 산업의 스마트화 추진 | <ul style="list-style-type: none"> <li>가전기업의 연구개발을 통해 스마트기기로 나아가고 서비스 능력을 제고</li> <li>자동차기업과 IT기업의 합작시스템을 구축하여, 스마트운전, 환경감지능력, 스마트설비 탑재 등 기술상품의 연구 개발과 응용을 가속화</li> </ul>                |

| 단말 상품의 스마트화 제고 | <ul style="list-style-type: none"> <li>이동단말 핵심기술의 연구개발 및 산업화 능력을 제고</li> <li>스마트 기술의 로봇 영역에서의 응용을 추진하여 로봇상품의 감지, 통제 등 분야에서의 성능과 스마트 수준을 제고</li> </ul>                                    |

출처: 한국지식재산연구원(2016.3.)

#### □ 주요국 대응전략 요약

<표 4> 주요국의 4차 산업혁명에 대한 대응전략 비교

| 구분       | 미국                                                                                 | 독일                                                                                                | 일본                                                                          | 중국                                                                           |

|----------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 민간과 정부역할 | <ul style="list-style-type: none"> <li>민간주도</li> <li>정부지원</li> </ul>               | <ul style="list-style-type: none"> <li>선 민간주도</li> <li>후 민관공동대응</li> </ul>                        | <ul style="list-style-type: none"> <li>민관 공동 주도</li> </ul>                  | <ul style="list-style-type: none"> <li>정부주도</li> <li>민간실행</li> </ul>         |

| 거버넌스     | <ul style="list-style-type: none"> <li>민간컨소시움</li> <li>민관컨소시엄</li> </ul>           | <ul style="list-style-type: none"> <li>선 인더스터리 4.0</li> <li>후 플랫폼 4.0</li> </ul>                  | <ul style="list-style-type: none"> <li>제 4차 산업혁명 관민회의 (정부/기업/학계)</li> </ul> | <ul style="list-style-type: none"> <li>정부 (국무원, 공업신식화부)</li> </ul>           |

| 핵심전략     | <ul style="list-style-type: none"> <li>신미국혁신전략</li> <li>AMP 2.0</li> </ul>         | <ul style="list-style-type: none"> <li>인더스트리 4.0</li> </ul>                                       | <ul style="list-style-type: none"> <li>제 4차 산업혁명 선도회의</li> </ul>            | <ul style="list-style-type: none"> <li>중국제조 2025</li> <li>인터넷플러스</li> </ul>  |

| 특징       | <ul style="list-style-type: none"> <li>기술/자금보유 글로벌기업 주도</li> <li>제조업 중심</li> </ul> | <ul style="list-style-type: none"> <li>제조업과 ICT 융합</li> <li>국제표준화 주도</li> <li>프로운호프연구소</li> </ul> |                                                                             | <ul style="list-style-type: none"> <li>제조업경쟁력 제고</li> <li>내수시장 중심</li> </ul> |

출처: 정보통신정책연구원(2017.5.)

### 3. 지능형 반도체 기술개발사업

#### 3.1 국내외 기술개발 동향

##### 가. 소프트웨어 기반 인공신경망 전용 반도체 동향

- (인공지능 SW프레임워크) DNN 구현을 위한 다양한 SW 프레임워크가 개발되어 배포되고 있으며, Caffe, TensorFlow, Torch, Theano 등이 있음

- Caffe : 가장 널리 사용되는 프레임워크로 페이스북에서는 모바일기기향으로 Caffe2Go와 같은 특화 버전을 개발하고 있음

- TensorFlow : 구글이 개발한 프레임워크로 Caffe 대비, 안정성 그리고 RNN<sup>4)</sup>을 지원하고 있으며, 구글에서 개발한 최신 뉴럴 네트워크(예, GoogLeNet v4)를 재사용하기 위해서 주로 사용됨

- 스마트폰 등 모바일 시스템 상의 뉴럴 네트워크 설계에 사용하기 위해 TensorFlow mobile 개발이 진행되고 있으며, 메모리 및 자원의 한계를 고려하여 8bit 데이터에 기반한 뉴럴 네트워크를 지원

- Torch : Lua 언어를 기반으로 한 머신 러닝용 프레임워크로 텐서에 대한 다양한 연산과 뉴럴 네트워크에서 사용하는 여러 연산들을 지원하며 NVIDIA에서 추가적인 확장 모듈을 개발하여 GPU 가속 지원하며 페이스북, IBM 등에서 지원

- Theano : Python 언어의 라이브러리 형태로 제공되는 머신 러닝 프레임워크로, 수식 및 행렬 연산을 도와주는 기능들을 다수 지원하여 기존 머신러닝 알고리즘 구현에 활발하게 사용

- Symbolic differentiation을 지원하여 텐서에 대한 수식을 기술하면 그에 대한 머신 코드를 자동으로 생성해냄

- NVIDIA® DIGITS : Caffe, Theano, Torch 등의 다양한 딥러닝 프레임워크를 보조해주는 도구로 웹 기반의 인터페이스를 구현하여 브라우저를 통해 뉴럴 네트워크의 구현 및 시각화를 편리하게 수행할 수 있음

- 뉴럴 네트워크 최적화를 위한 다양한 알고리즘 개발이 활발히 진행되고 있음

- 알고리즘 최적화 기술인 모델 압축(model compression)은 행렬 근사에 기반한 저차원 근사 기법(low rank approximation)과 크기가 작은 데이터에 대한 연산을 하지 않는 제거 기법(pruning)으로 분류되며 다양한 연구가 진행 중임

- 페이스북과 뉴욕대에서는 2014년 truncated SVD<sup>5)</sup> 방법을 적용하여 정확도는 유지하면서 fully connected layer의 모델 크기를 크게 줄일 수 있다고 발표한 이후 저차원 근사 기법에 대한 활발한 연구가 진행 중

- 최근 마이크로소프트에서는 저차원 근사 기법으로  $D \times D$  행렬연산을  $D \times 1$ ,  $1 \times D$ ,  $1 \times 1$ 으로 분

4) Recurrent Neural Network

5) Singular Value Decomposition

리하여 계산량을 줄이는 기술을 제안함

- 제거 기법은 뉴럴 네트워크 연구 초기부터 제안된 방법이나 2016년 스탠포드대에서 처음으로 대규모 뉴럴 네트워크에 적용 가능한 방법을 제안한 후, NVIDIA, Baidu 등에서 실적용 준비 중

- 양자화 기술은 CPU, GPU를 위한 양자화와 하드웨어 가속기를 위한 양자화로 분류되며, 최근 개발되는 CPU, GPU에서 지원하는 8bit 단위 연산을 활용하기 위한 정수형 행렬 연산을 서버 향 CUDA 라이브러리 뿐 아니라 TensorFlow Mobile 등 모바일 향 NN 프레임워크에서도 지원하기 시작

- 하드웨어 가속기는 8bit 미만의 저정확도 연산(low precision arithmetic)을 지원하는 장점이 있으며, 이러한 저정확도 연산을 갖는 뉴럴 네트워크 최적화 방법에 대한 연구가 외국 기업과 대학 연구소에서 활발히 진행되고 있음

- Allen Institute for AI와 뉴욕대에서는 XNOR-Net을 제안하였는데, AlexNet의 경우 binary (1bit) weight를 사용할 경우에도 정확도가 그대로 유지되는 결과를 발표함 (2016.08)

- 중국의 딥러닝 기술 기업인 Face++에서는 1bit weight, 2bit activation으로도 AlexNet 정확도 저하가 10% 이내로 적다고 발표함 (2016)

□ 국내에서는 삼성전자가 기존의 Caffe를 기반으로 설계된 뉴럴 네트워크를 저차원 근사 방법으로 최적화하고 스마트폰 등 모바일 디바이스 상에서 수행할 수 있는 OpenCL 코드를 생성하는 환경인 S-DNN을 개발하였으며, 알고리즘 최적화 연구는 다양한 기업, 학교에서 활발하게 진행 중

- 인텔 물체판별 알고리즘으로 PVANET을 제안하였는데, 이는 기존 최고 알고리즘인 ResNet 기반 Faster R-CNN 대비 1% 정도의 정확도 손실로 40 배의 계산량 감소가 가능하다고 보고 함 (2016.12)

- 삼성전자에서는 저차원근사 방법으로 Tucker 방법을 적용하여 AlexNet의 경우 Galaxy S6 상의 실측 결과로 3배 이상 에너지를 감소시킴 (2016.05)

- 고려대학교 등에서는 뇌-컴퓨터 인터페이스 (BCI, Brain-Computer Interface) 기술과 접목하여 뇌 신호를 이용한 다양한 응용에 적용하는 연구를 진행 중

- 고려대학교에서는 뇌-컴퓨터 인터페이스 연구에 인공지능 기술을 적용하여 사용자의 의도를 더 정확하게 인지할 수 있도록 temporal, spectral, spatial 정보를 해석하는 데에 딥러닝 을 적용한 연구결과를 발표

<그림 9> 딥 러닝이 적용된 뇌-컴퓨터 인터페이스

(출처: 고려대학교 이성환 교수 연구실)

<그림 10> 딥러닝을 활용한 뇌신호 분석

(출처: 고려대학교 이성환 교수 연구실)

- 보행 환경에서 딥 뉴럴 아키텍처를 기반으로 사용자의 의도를 정확하게 인지하는 실시간 BCI 시스템을 개발한 바 있으며 일반적으로 BCI의 정확한 인지 성능을 위해서는 사용자에 따른 calibration 과정 또는 pre-training 과정이 필요한데, 이와 관련하여 Bayesian framework를 기반으로 calibration 과정을 줄인 zero-training BCI도 함께 연구된 바 있음

- BCI 뿐만 아니라, 구체적으로 뇌 신호 분석에 딥러닝을 적용한 연구결과들도 발표되었는데 이는 뇌파 측정에 있어서 다양한 잡음에도 불구하고 뇌파의 패턴을 확인하는 데 CNN 아키텍처를 적용했음

- 또한 뇌 관련 질병의 진단과 뇌 신경망 분석을 위해 기존 방식에서 더 나아가서 머신 러닝을 적용한 연구 결과를 발표한 바 있고, 뇌에서 발생한 신호뿐만 아니라 EMG (electromyogram) 신호를 기반으로 사용자의 의도를 분석하여 인공 팔을 움직이는 데에 딥러닝 아키텍처를 적용하여 연구 결과를 발표한 바 있음

- 서울대에서는 fixed point 양자화 기술을 개발하여 RNN에 적용하였으며(2015), 딥러닝을 위한 메모리 중심 칩 아키텍처를 연구 (2017.2)

- 기존의 아키텍처에서 심화학습 실행의 효율성을 높이는 연구를 진행 중에 있으며, 향후 심화학습을 목표로 하는 새로운 칩 아키텍처를 개발할 계획

- 기존 아키텍처의 메모리 액세스에 많은 에너지를 소비하는 것을 개선하고 최대한 성능을 유지할 수 있는 효율적으로 작동할 수 있게 하는 것임

- 지능정보 처리 기술의 다양한 서비스 적용을 위해서는 방대한 연산 자원을 요구하는 이론적 인공지능 알고리즘 연구와 더불어 반도체에 적합한 실용적 알고리즘 개발이 필요함

- 네이버에서는 음성에 대한 인식 및 처리를 위해 딥러닝 기술 활용을 통한 상업적인 서비스를 시작 하였으며, 딥러닝(Deep learning) 기술의 개발과 대용량 음성 데이터베이스의 활용을 통해 음성인식 기술이 사람의 인식 능력을 능가하는 수준까지 도달

- 현재의 인공지능 알고리즘 연구는 빅데이터를 기반으로 각 응용 분야별 학습을 통한 음성, 영상, 패턴 등을 각각 인식하고 분석하는 방식에서 음성, 영상, 신호를 동시에 함께 학습하는 멀티 모달리티 방식으로 진화하고 있는 추세임

- ETRI에서는 국내 인공지능 알고리즘의 대표적 연구로는 엑소브레인 프로젝트이며 전문가 수준의 지식 소통이 가능한 인공 지능 시스템을 개발하여 장학퀴즈에서 사람과의 대결에서 우승을 차지(2016. 11.)

- 엑소브레인 프로젝트는 기계와 인간의 의사소통을 뛰어넘어 전문 직종의 전문가 수준의 지식 소통이 가능한 인공두뇌 SW 기술 개발이 목표

※ ETRI, 솔트룩스, KAIST 등 27개 기관이 참여하여 2023년까지 수행

<그림 11> ExoBrain 프로젝트 구성도 및 장학퀴즈 대결

- 또한 ETRI에서는 대규모 이미지 및 동영상 분석을 통해 상황을 이해하고 위험 예측을 실시간으로 수행하는 대규모 시각 빅데이터 분석 및 예측 인공지능 알고리즘 개발 진행

- 딥러닝 프로젝트는 사진과 동영상을 통해 의미와 상황을 이해하고 예측하는 사람수준의 시각 지능 알고리즘 개발이 목표

※ ETRI, 포항공대 등 29개 기관이 참여하여 2024년까지 수행 예정

- 서울대에서는 뇌 정보처리 과정을 모델링 하여 기계 학습 기반으로 사용자 의도 예측 기술을 연구하고 이를 발전시켜 스토리 창작과 같은 고차원적 인공지능 기술을 연구 개발

- 포항공대는 “평생 기계학습 연구센터”를 설립하여 4년간 (2014~2018) 기계학습 플랫폼 개발하고, 기계학습 연구센터의 주요한 목표는 국내 머신러닝 연구 생태계를 만들고 일반 사용자도 쉽게 사용할 수 있는 머신러닝 공개SW를 개발함

- 대량의 데이터를 활용한 다수 사용자의 인공지능 학습 연구를 가속하기 위한 FPGA 기반의 서버용 모듈 기술 개발을 진행 중

- 뇌과학 분야와 ICT 기술의 융합을 통해 새로운 인공지능 모델을 만들고 이에 대한 학습 및 활용에 대한 알고리즘과 하드웨어 가능성 연구 분야 추진

- KAIST에서는 HTM\* 모델을 이용한 새로운 지능정보 처리 기술의 구현을 위해 인공신경망 칩을 설계하여 발표

※ 김덕환, 송지훈, 신영수, “Hierarchical Temporal Memory 방식을 이용한 뇌 인지 기능 모사 하드웨어 구현,” 제19회 한국반도체학술대회

- 한동대에서는 기계 학습 기반의 딥러닝을 이용한 문자 인식 기술을 통해 기존 고전적 기술 대비 획기적인 성능 개선 결과를 발표

- 의료 데이터베이스 기반의 CNN 신경망 학습 기술을 개발하여 의료 영상 기반의 질병 진단 보조 기술을 개발 ('루닛', 백성욱)

□ (국내 인공지능 반도체 병렬프로세서 기술의 동향) 프로세서 코어 설계 기술, 컴파일러, 지능정보처리 SW 기술 등의 핵심기술은 갖추고 있는 반면, 매니코어 프로세서 핵심기술은 부족

<표 5> 국내 프로세서 관련 기술 개발 실적

| 매니코어핵심기술                                                                                                                  | 대표 성과                                            | 세부내용                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 시각지능 인지프로세서 ('16~'19)<br>                | 사람수준의 인지 능력을 밀리와트급의 에너지로 실현하는 반도체 개발             | <ul style="list-style-type: none"> <li>0 100종 이상의 범용객체를 사람의 지능 수준으로 인지하고 mW급의 에너지를 통해 모바일 장치에서 활용 가능한 시각지능 전용 칩을 실현</li> </ul>                                                                             |

| 멀티코어프로세서 (Aldebaran, AB) ('07~'16)<br>   | 프로세서 기술 차립 및 고성능 멀티코어 기술 자체확보                    | <ul style="list-style-type: none"> <li>0 프로세서 아키텍처 독자개발 및 국내 대기업 초미세공정(28nm) 개발을 통한 프로세서 원천기술 확보</li> <li>0 세계 최고 수준의 에너지 효율을 보이는 프로세서 기술 확보</li> <li>0 퀘드코어, 영상처리IP, 특징점 추출에 의한 인식기능을 통합한 프로세서</li> </ul> |

| 초소형 신호처리 프로세서 (EMP) ('06~'10)<br>       | 영상, 음성 등의 신호를 효율적으로 처리하기 위한 저전력 초소형 프로세서 및 SW 개발 | <ul style="list-style-type: none"> <li>0 초소형 저전력 임베디드 DSP(Digital Signal Processor) 프로세서 개발 및 기술보급에 의한 다수 양산품 개발</li> </ul>                                                                                |

| 에너지 스케일러블 벡터 프로세서 (ESVP) ('10~'13)<br> | 세계최고 수준 에너지 효율성을 가지며 다수코어로 확장가능한 벡터 프로세서         | <ul style="list-style-type: none"> <li>0 차세대 프로세서 아키텍처 기술을 확보하기 위한 옥타코어(8개)급 에너지 자율제어형 모바일 멀티프로세서와 병렬컴파일러 기술 개발</li> </ul>                                                                                 |

- 매니코어 프로세서는 지능정보 처리의 고성능 프로세싱을 요구하는 응용 및 서비스가 등장하면서 각광을 받고, 해외 글로벌 기업은 자사의 기술을 재사용 형태로 개선하는 반면, 국내는 설계 관련 기술이 부족한 상황

- 환경적인 요소에도 불구하고 국내 프로세서 관련 원천기술은 연구소, 기업, 학계를 중심으로 꾸준히 개발되어 왔으며, 최근 성과를 거두고 있음

- 반도체 공정 스케일링의 한계에 따른 성능향상 한계를 극복하기 위한 방안 중의 하나인 병렬 컴퓨팅 기술은 2000년대 초부터 장기간 연구가 진행되었으며, 최근 딥러닝 기술의 발전과 더불어 주목을 받고 있음

<그림 12> SW26010

(출처: Sunway report, 2018)

- 지능정보 프로세싱을 위한 정부 차원의 정책적인 지원을 바탕으로 전세계 글로벌 기업의 매니코어 프로세서 기술 선점을 위한 연구가 활발히 진행되고 있으며, 특히 중국은 CAS(국가과학원, Chinese Academy of Science)를 중심으로 연구 개발을 진행하고 있으며, 자체 개발한 매니코어 프로세서 SW26010을 적용한 슈퍼컴퓨터 “Tailhulight”를 개발하였음

- 매니코어 프로세서 SW26010 40,960개를 장착한 Sunway Taihulight 슈퍼컴퓨터는 2018년 전세계에서 가장 빠른 슈퍼컴퓨터로서 최대 지속 성능은 93.01 페타플롭스, 피크 성능은 125.44 페타플롭스, 전력 효율은 와트당 6.051 기가플롭스임

- 중국은 Tailhulight보다 10배 더 빠른 수퍼컴을 개발하고 있음

- Jiangnan Computing Lab에서 SMIC 공정에서 1400MHz의 동작주파수를 가질 수 있는 (Sunway SW-2) 64-bit RISC 기반 Processor ISA를 개발하였으며, SW26010은 이 아키텍처를 기반으로 National High Performance Integrated Circuit Design Center에서 개발되었고, 260개의 코어를 장착한 매니코어 프로세서임

- (DNN 가속 반도체) 글로벌 기업은 최근 큰 주목을 받고 있는 딥러닝 기반의 인공지능 반도체 개발을 위하여 정부의 지원과 시장 지배력을 바탕으로 지능정보 처리를 위한 다양한 아키텍처의 프로세서를 개발하고 있음

- NVIDIA는 자사의 그래픽스 처리 프로세서(GPU) 기술을 기반으로 ADAS<sup>6)</sup> 프레임워크를 개발하고 있으며, 그래픽스 기능의 핵심인 쇼이더 코어를 응용하여 딥러닝 구현

- 2000년대 초반, 기하쉐이더(Geometry Shader)와 픽셀쉐이더(Pixel Shader)의 개념을 처음으로 도입한 NVIDIA는 통합쉐이더(Unified Shader)로 전세계 그래픽스 시장을 장악하였으며, 그 원천 기술은 작은(Small), 다수의(Many) 코어를 L1 캐시와 L2 캐시로 상호 연결한 프로세서 기술임

- 그래픽 처리 중심의 프로세서로 기술개발을 시작하였으나 2000년대 중반부터 작은 코어를 여러 개 탑재한 매니코어 구조의 GPU 구조에서 GPGPU라는 개념을 발전시켰으며, 이를 기반으로 다양한 어플리케이션에 적용함

6) Advanced Driver Assistance System

- 기존의 ADAS는 몇몇 물체 감지 및 단순한 분류 작업, 도로의 위험 상황에 대한 알림, 감속 또는 정지 기능 정도만 가능했으나, 현재의 ADAS는 사각지대 확인, 차선 변경 전면 추돌 경고 기능까지 추가됨

<그림 13> ADAS 기능 예

- NVIDIA는 딥러닝 기술을 활용하여 NVIDIA DRIVE™ PX2를 개발하고 DriveWorks라는 자율주행 소프트웨어 개발킷이 포함되어 있어 NVIDIA Self-Driving Car Solution을 통해 경찰차와 택시, 구급차와 택배 트럭, 주차된 차와 진입 중인 차를 구별할 수 있고, 자전거와 보행자까지 구별가능

<표 6> 자율 주행을 위한 NVIDIA의 프로세서 기반 시스템

| AUTOCRUISE 용 플랫폼          |                                                                         |

|---------------------------|-------------------------------------------------------------------------|

| 고속도로 자율주행 및 HD 맵핑 처리기능 탑재 |                                                                         |

| AUTOCHAUFFEUR 용 플랫폼       | 2개의 SoC와 2개의 GPU로 구성되어 있고, 출발점-도착점 설정 후의 주행을 위해 설계됨                     |

| 멀티시스템 구조도                 | 여러 개의 DRIVE PX 2로 구성된 시스템으로서 다수의 시스템에서 확보된 연산처리 성능을 완전 자율주행에 응용하기 위한 개념 |

- 확장성 있는 구조로 수동 냉각식 모바일 프로세서부터 2개의 개별 GPU가 있는 멀티칩까지, 완전한 자율주행을 위해 여러 개의 플랫폼을 병렬로 사용하는 등 다양한 구성이 가능함

- CES 2017에서는 아우디의 Q7 모델과, 테슬라의 Tesla Model S 등 NVIDIA DRIVE™ PX 2를 활용한 자율주행 차량들이 공개됨

- CES 2018에서는 NVIDIA는 세계적인 자동차 제조업체인 폭스바겐, 중국 시장에서의 바이두와 세계적인 자동차 부품 공급업체인 ZF와의 협업, 라이드 쇼어링 기업 우버와 자율주행 분야 선도 스타트업 오로라와 협력을 발표

- o 인공신경망 알고리즘은 생물학의 신경망을 모델로 만들어진 학습 알고리즘으로 최근에는 2개 이상의 층으로 구성된 MLP (Multi Layer Perceptron) 중에서 8개 이상의 많은 층으로 구성된 DNN이 활발히 연구됨

- DNN의 경우 대부분 십만 개 이상의 뉴런으로 구성되어 있어 연산량이 방대하지만 간단한 연산들이 반복되고 병렬성이 높기 때문에 다수의 코어를 보유하고 있는 GPU에서 효율적인 연산이 가능함

- NVIDIA사는 인공신경망 연산 전용 라이브러리 cuDNN을 제공하고 다양한 인공신경망 플랫

폼(TensorFlow, Caffe 등)들을 지원하며 가장 최근에 개발된 GPU 아키텍처는 파스칼 아키텍처로 공정이 기존 맥스웰(GM200)에서 24개였던 SM(Streaming Multiprocessor) 수가 56개(GP100 기준)로 늘어나 더 높은 성능을 보임

<그림 14> 파스칼 SM 아키텍처

<그림 15> Google의 TPU

- 시스템 상에서의 성능 관련 가장 큰 변화는 부동소수점 연산으로 Single-precision 연산 성능이 10.6TFLOPS로 맥스웰 대비 1.5배 향상됐으며 Double-precision 연산은 5.3TFLOPS 성능을 나타내며 DNN 연산에 널리 쓰이고 있는 Half-precision 연산 성능은 21.1TFLOPS로 개선

- 또한 NVIDIA는 GPU Technology Conference(GTC) Europe에서 자율 주행차를 위한 AI Supercomputer chip, Xavier을 발표함

- 512 개의 Core로 구성된 Volta Architecture 기반의 GPU, 8개의 Core로 구성된 Custom ARM64 CPU, 새로운 CVA(computer vision accelerator), 그리고 Dual 8K HDR를 지원하는 Video Processor로 구성이 되어 있고 20 TOPS<sup>7)</sup>의 성능을 나타내면서 약 20W 전력을 소모

- 자율주행차를 위한 칩이기에 차량용 안전 기준 표준인 ISO26262 functional safety specification의 ASIL C 수준의 Functional Safety를 만족

<그림 16> Xavier Chip 구조 및 개발 보드 (출처: GTC Europe 2016)

- 구글은 SW 및 빅데이터 센터 기반으로 인터넷 서비스를 전문으로 하는 기업이나 자사의 빅데이터 센터에 사용되는 서버를 기반으로 인공지능 등을 필요로 하는 특수 서비스의 필요성이 증대되면서 2015년 프로세서 반도체를 개발하기 시작

- DNN리서치(DNN Research), 딥마인드(DeepMind), 무드스톡(Mood stocks) 등 머신러닝 기술 기업을 인수하여 내부 역량을 쌓아왔으며 2016년 3월 구글 딥마인드 챌린지 매치에서

7) Trillion Operations Per second

인공지능(알파고)이 바둑에서 프로기사를 처음 이기는 성과를 거둠

- 2016년 5월에 데이터 분석과 딥러닝을 위해 개발한 TPU(Tensor Processing Unit)을 공개

- 내부 아키텍처는 공개되지 않았지만 GPGPU보다 벡터/행렬연산의 병렬처리에 더 특화되어 있으며 8비트 정수 연산을 활용한 것으로 알려졌음

- 2017년에는 기존의 TPU를 개선하여 학습에도 사용할 수 있는 Cloud TPU와 이를 기반으로 한 TPU Pod을 발표하였음

- 인텔은 모바일 시장에서 실패한 이후, 대형, 고속의 데이터 센터 서버용 프로세서에 집중하여 다양한 프로세서 제품군을 생산 중

- 2016년 제온 파이(Xeon Phi) 7200 시리즈를 소개하였고 제온 파이는 MIC(Many integrated core) 아키텍처로 칩 하나에 64~70개 이상의 코어를 탑재해 병렬 처리를 높였고 이전 세대와 달리 보조 프로세서가 아니라 운영체제를 부팅할 수 있으며 프로세서 하나에 3TFLOPS의 연산력을 보유

- 2015년에는 FPGA(Field Programmable Gate Array) 선두 제조업체인 알테라(Altera)를 인수하여 FPGA의 시스템 설계자가 요구하는 대로 칩 구성이 가능하다는 장점을 이용하여 자동차, 사물인터넷(IoT), 인공지능처럼 용도에 맞게 커스텀 프로세서를 제공

- 2016년에는 인지컴퓨팅 업체 사프론, 비전 프로세싱 솔루션 업체 모비디우스, 딥러닝 전문 업체 너바나 등을 인수하였고, 특히 너바나를 통해 차후 출시되는 인텔 제온과 제온 파이 프로세서의 딥러닝 성능을 강화할 예정

- 2017년 AI 프로젝트와 관련 작업용으로 너바나 NNP(Nervana Neural Network Processor)를 공식 발표 함(17.10)

- 퀄컴은 뇌모방 컴퓨팅을 위한 프로젝트인 제로스(Zeroth)를 발표하였으나, 현재는 완전한 DSP(Digital Signal Processor, 디지털 신호처리 프로세서) 중심의 뉴럴넷 컴퓨팅용 환경을 제공하는 형태로 개발 방향을 전환

- 퀄컴의 뉴로모픽칩 개념인 NPU(Neural Processing Unit) 제로스(Zeroth)는 스냅드래곤 820에 내장되었으며 기계 학습 기술에 사용되었고 2016년에는 제로스 플랫폼을 지원하는 스냅드래곤 뉴럴 프로세싱 엔진 SDK를 개발 배포하였음

- 2017년 1월 스냅드래곤835를 공개했고, 크라이요 280(CPU, 아드레노 540 GPU, 헥사곤 682 DSP에 Gbit급 다운로드를 제공하는 X16 롱텀에볼루션(LTE) 모뎀칩을 10나노 핀펫 미세공정으로 개발하였으며 단말기에서의 인공지능 지원을 위해 헥사곤 코어는 구글의 TensorFlow를 지원

- Snapdragon 820 Series Processor에 NPU(Neural Processing Unit)을 통합하여 고도의 지능형 컴퓨팅을 위한 Machine Learning 알고리즘 가속을 위한 SDK를 제공(Embedded Vision Summit 2016에서 발표)

- Nauto와 협력하여 Zeroth를 이용한 인공지능 센서를 만들고 있으며, 이 센서는 충돌 위험을 분석, 운전자의 행동 등을 기록함

<그림 17> Snapdragon 835 Block Diagram

- 2017년 12월 스냅드래곤 845는 전작 대비 보안과 연결성, 그리고 인공지능(AI) 기능이 강화됐음. 그래픽 속도와 전력 효율성은 30% 향상됐고, 디스플레이 처리 속도는 2.5배

- 공개된 스냅드래곤 845의 세부 사양은 ▲X20 롱텀에볼루션(LTE) 모뎀 ▲헥사곤(Hexagon) 685 디지털 신호 프로세서(DSP) ▲크라이오(Kryo) 385 중앙처리장치(CPU) ▲어쿠스틱 오디오(aqstic audio) ▲아드레노(Adreno) 630 그래픽처리장치(GPU) ▲스펙트라(Spectra) 이미지 신호 프로세서(ISP) 등이 있음

<그림 18> 자동차용 Nauto (출처: Nauto, <http://www.nauto.com>)

- CEVA, Inc.는 전통적인 DSP나 최근 병렬처리 중심의 뉴럴넷 구조 연구를 위하여 CEVA DSP MX 시리즈에 해당 서비스를 구현하고 솔루션 전체를 제공

- 3D 비전, 컴퓨터 활용 사진 기술(computational photography), 시각적 인지 및 분석을 지원

- CDNN(CEVA deep neural network) toolkit은 네트워크 생성기, 소프트웨어 프레임 워크 및 하드웨어 가속기로 이루어지며 네트워크 생성기는 풍부한 자원의 PC 환경에서 인기있는 Caffe와 같은 딥 러닝 프레임 워크에서 미리 학습된 부동소수점 방식의 인공신경망 정보를 임베디드 시스템에 적합하도록 고정소수점 방식의 수정된 인공신경망 정보로 변환시킴

- 고정소수점 방식의 수정된 인공신경망 정보는 임베디드 시스템에 전달되어 실시간 신경망 라이브러리로 구성된 소프트웨어 프레임 워크 및 하드웨어 가속기를 통해 컴퓨터 비전 기능을 수행함

<그림 19> CEVA DNN의 동작 개념 (출처: BDTI, Inc., '16 )

- 중국과학원 CAS(Chinese Academy of Science)에서는 딥러닝 분야에서 머신러닝 가속기 개발을 목표로 “DianNao”를 개발

- 한정된 면적으로 성능 및 에너지 효율을 최적화하여 인공신경망 알고리즘을 실행 가능한 가속기를 설계하는 것이 목표

- 중국과학원 CAS(Chinese Academy of Science)에서 육성한 한우지(寒武紀)과학기술회사는 2017년 11월 차세대 인공지능 칩을 발표함. 대뇌의 신경세포와 신경연쇄를 본따 하나의 명령으로 한개 그룹 신경세포의 처리를 완성할 수 있어 이런 컴퓨팅 패턴은 이미지식별 등 스마트 처리를 진행하는 효율이 전통 칩보다 수백 배 높다고 함

- DianNao는 기존의 머신러닝 가속기의 경우 알고리즘의 연산부분을 효율적으로 처리하기 위하여, 메모리의 성능 및 소모 에너지 최적화에 중점을 둔 CNN 및 DNN 가속기로 설계하였으며, 128-bit 2GHz SIMD processor에 비해 117.87배 빠른 연산성능과 21.08배 향상된 에너지 효율을 보임

- 인공신경망 알고리즘이 점차 많은 양의 데이터를 복잡한 과정으로 처리하도록 발전함에 따라 multi-chip으로의 확장에 대한 연구 결과인 DaDianNao를 발표하였으며, NVIDIA K20M GPU에 비해 450.65배 빠른 연산성능을 얻을 수 있으며 에너지 효율 또한 150.31배 만큼 개선되는 효과를 나타내었음

- 복수의 머신러닝 기법을 활용하는 응용을 지원하기 위하여 다양한 머신러닝 기술을 사용 가능한 PuDianNao를 발표하였으며, 머신러닝을 활용하는 이미지 응용에서의 실행 성능 및 에너지 효율 최적화를 위하여 CNN에 특화된 형태의 머신러닝 가속기 ShiDianNao가 제안

<그림 20> Cambricon ISA 및 Pipeline Architecture (출처: ISCA 2015)

- 다양한 종류의 신경망 기술을 동시에 지원을 목표로 instruction set 수준의 유연성 및 효율성을 위한 신경망 가속기를 위한 Instruction Set Architecture (ISA) Cambricon이 제안되었고, Cambricon을 활용하여 신경망 기술을 활용할 경우 코드 길이가 GPU, x86, MIPS에 비해 각각 6.41배, 9.86배, 13.38배 압축되는 효과를 얻을 수 있음

<그림 21> Cambricon Chip Area & Power Summary

- Intel은 Movidius 인수 1주년을 맞아, 새로운 칩 Myriad X 발표(17.9)

- 모비디우스는 ISAAC, Myriad 1 개발을 통해 2016년 2월 Many-core Vision Processing Unit인 Myriad2를 발표하였음

<그림 22> Myriad2 칩과 SHAVE VLIW프로세서 구조 (출처: HotChips '14)

- 특정 비디오 처리 작업을 가속하기 위한 Atomic Imaging/Vision Engine, Multi-ported Scratched Memory인 Intelligent Memory Fabric, 128-bit Vector VLIW Processor인 SHAVE(Stream Hybrid Architecture Vector Engine), 그리고 UltraSPARC ISA Processors로 구성되었으며 Heterogeneous Architecture를 가지는 VPU(Vision Processing Unit)인 Myriad 2를 개발함

<그림 23> Myriad 2 Software Stack

(출처: Hot chips 2014)

- Myriad 2를 위한 Software Development Kit를 제공하며 Imaging/Vision Engine에서 수행되는 기능, Vision Software Library, 그리고 Developer Own Function을 Atomic Imaging/Vision Engine, Intelligent Memory Fabric, Vector VLIW Processor에 최적화하여 할당함

- VLIW프로세서와 온칩 뉴럴넷 메모리를 통합한 형태의 기술을 응용하여 휴대폰, HMD(Head Mounted Display) 등에서 활용이 가능한 Vision Application을 제공

- 개발된 칩은 TSMC 28nm HCMOS LP process로 제작되어 1W의 전력을 소모하며 80~150 GFLOPS의 Video Processing 컴퓨팅 능력을 보이는 것으로 발표

- Nervana사는 부동소수점 컴퓨팅 아키텍처의 해상도의 동적 변화에 의하여 초병렬의 컴퓨팅을 구현하고자 설립되었으며 자체적으로 “Nervana Engine”을 개발하였고, 현재 인텔에 인수되어 개발을 지속하고 있음

- Python 기반의 Deep Learning Library 이자 Caffe와 같은 딥 러닝 프레임워크인 Neon을 개발함

- Neon은 Python 기반의 Deep Learning Model을 위한 Library로써 Theano, Caffe와 같은 다른 딥 러닝 프레임워크와 비교하여 2배 이상 빠름

- 이를 위해 Neon은 Assembler-level 최적화, Multi-GPU 지원, 최적화된 Data Flow, 그리고 딥 러닝 모델에서 많이 사용되는 Convolution 연산을 위해 Winograd 알고리즘을 이용하고 있음

- Neon, 딥 러닝 프레임워크를 가속하기 위한 딥 러닝 ASIC인 Nervana Engine을 개발하고 있으며 지금까지 공개된 구조로는 HBM을 이용한 3D Memory Stack과 Interposer 기술을 이용하여 빠른 외부 메모리 접근을 하도록 함

- Data는 16-bit로 저장하고 Precision을 높을 수 있는 FlexPoint 기술, Software-based Data Control을 통한 Compute Density를 높였고 병렬화를 높이기 위한 Pipeline Isolation, Six Bi-directional High-bandwidth Links를 통한 칩간 통신 병목 해결을 통해 NVIDIA의 Maxwell Architecture기반 GPU를 장착한 Titan X 보다 10배 더 빠르게 수행할 수 있는 것으로 알려짐

<그림 24> Neon과 Caffe간의 Computing Time 비교

- 경량의 뉴로모픽 엔진을 모바일 또는 소형 프로세서에 탑재하기 위하여 글로벌 기업을 중심으로 연구 개발 진행 중

- 애플은 A11 바이오닉스 프로세서에 뉴럴 엔진을 추가하였음

- 뉴럴엔진은 기존의 GPU와 함께 FaceID와 애니모지 등을 처리하기 위하여 듀얼코어로 이루어져 있으며 600 GOPS의 성능을 가짐

- 아이폰X에 장착된 A11 바이오닉스는 2개의 고성능 CPU, 4개의 고효율 CPU, 3개의 GPU, ISP 유닛 및 뉴럴엔진을 포함

- A11 바이오닉스 프로세서는 TSMC 10nm FinFET 공정을 사용하여  $8197 \times 10674 \text{ um}^2$ 의 면적을 가짐

<그림 25> 애플의 A11 바이오닉스 프로세서

- 화웨이는 Kirin 970 프로세서에 NPU (Neural Processing Unit)을 장착

<그림 26> 화웨이의 Kirin 970

- NPU는 1.92 TFLOP의 성능을 갖고 온-디바이스 AI를 담당하며 클라우드 AI와 결합하여 지능형 디바이스가 가능

- 메이트10에 장착된 Kirin 970은 8개의 CPU 코어 와 12개의 GPU 코어, 듀얼 ISP 유닛 및 NPU을 내장함

- Kirin 970은 TSMC 10nm 공정을 사용하여 약 1 cm<sup>2</sup>의 면적을 가짐

- NPU는 AI 업체인 캠브리콘 기술의 지적재산을 라이선스한 것으로 ISA구조를 가짐

- 전 세계적으로 4차 산업혁명의 흐름과 함께 인공지능 기술의 중요성이 높아지고 관련 기술이 발전함에 따라 요구되는 프로세서의 연산 성능이 크게 증가함에 따라 매니코어 및 뉴럴 코어와 같은 새로운 반도체 설계 기술이 요구되고 있음

- 최근 영상기반 객체인식을 위한 신경망 기술은 지속적으로 더 많은 신경망 층을 활용하고 있으며 이에 따라 연산량은 기하급수적으로 증가하고 있음

<그림 27> 영상기반 객체인식용 인공지능신경망 층수 추세

- 2014년도 옥스퍼드 대학교에서 발표한 VGG (Visual Geometry Group) 신경망의 경우  $138 \times 106$ (1억 3천 8백만)개의 파라미터를 이용하여 150억 번의 신경망 연산을 수행하여 약 90%의 정확도로 일상 사물 객체를 인식하였음

- 위의 객체 인식을 30ms 정도에 수행하기 위해서는 500GSOP/s<sup>8)</sup>의 연산 성능이 필요하여 기존의 프로세서 반도체 기술을 뛰어넘는 새로운 칩이 필요함

- ※ 기존의 프로세서를 사용하여 VGG 신경망을 운영할 경우 약 300~400Watt의 전력을 소비하며 한번 인식에도 ~수백ms의 시간이 소요됨

- 현재의 인공지능 기술은 방대한 연산량과 소비에너지 등의 문제로 대용량의 서버나 클라우드 기반 HPC를 기반으로 운영되고 있는 실정이며 다양한 응용과 모바일 환경 등으로의 확산을 위해서는 전용의 반도체 기술 개발이 필수적임

- 구글과 스탠포드 대학교에서는 1천만장의 유튜브 영상을 이용한 기계학습을 통해 머신이 스스로 고양이와 같은 객체를 학습하는 기술을 발표하였으며 이 기술은 1000대의 서버와 16,000개의 프로세서를 사용하고 약 1.6MWatt의 소비전력을 사용(ICML 2012, Andrew Ng, Google)

- 실용적인 인공지능 시스템을 만들기 위해 3대의 고성능 서버(1개 서버에는 4개의 GPU, 2개의 쿼드코어 CPU 포함)를 활용한 시스템을 발표함. 학습 시간은 늘어나지만 에너지 및 비용 등의 면에서 실용적임을 발표하였으나 1.5kWatt의 전력을 소비(ICML 2013, Andrew Ng)

<그림 28> 최근의 인공지능용 하드웨어 시스템의 형태 및 소비 에너지

- 알파고로 알려진 구글의 인공지능 시스템은 방대한 지능정보 연산량의 처리를 위해 1200개 이상의 CPU와 176개의 GPU를 사용한 것으로 알려져 있으며 내부적으로는 TPU (Tensor Flow Unit)라는 지능정보 처리 전용 칩이 포함된 연산 모듈을 개발하여 활용하는 것으로 발표

- 구글 선다 피차이 CEO는 구글 IO 2016 기조 연설 마지막 부분에서 머신러닝에 관해 발표하면서 최초로 TPU를 공개하였으며 내부에는 텐서플로우라는 구글의 기계학습 프레임워크에 최적화된 신경망 연산 전용의 반도체 칩이 포함되어 있음 (2016, 구글)

8) SOP/s: Synaptic Operations per Seconds, 초당 가능한 신경망 연산수

- 구글 선다 피차이 CEO는 다보스 포럼 연단에서 "인공지능(AI)은 인류가 이때까지 얻으려고 노력해온 것 중 가장 중요한 것"일 수 있다고 연설(18.1)

- 최근 DRAM 공정 기반의 PIM 기술에서 발생하는 성능저하 문제를 해결하기 위해 SRAM 혹은 차세대 메모리를 프로세서와 하나의 단위로 구성하는 PIM 구조들이 연구되고 있음

- 삼성전자가 메모리 반도체의 구조적 한계를 극복하기 위한 중장기 프로젝트로 최근 인스토리 지프로세싱(In Storage Processing·ISP) 기술 연구를 본격화('18.2)

- Micron에서는 DRAM 공정을 이용해서 오토마타 처리를 위한 프로세서와 메모리를 하나의 칩에 집적함

<그림 29> Micron의 오토마타 프로세서 (출처: ISC 2013)

- Venray에서도 DRAM 공정을 이용하여 프로세서와 메모리를 집적한 TOMI(Thread-Oriented Microprocessor)를 개발함

- 3개의 메탈층만으로 64비트 RISC 프로세서를 설계하였으며, 높은 성능을 얻을 수 없는 대신 전력 소모를 최적화하는데 초점을 맞춤

- 시스템을 구성하는 각 프로세서는 3-D 토러스 네트워크로 서로 연결되며, 서로 다른 DIMM은 온 칩 DDR 트랜스시버를 이용해서 연결함

<그림 30> Venray의 TOMI (2012-2014)

- UIUC(University of Illinois, Urbana-Champaign) 팀은 SRAM과 프로세서를 이용한 PIM 구조를 IEEE ICASSP 2015에서 발표하였으며 완벽한 PIM 구조는 아니지만 SRAM의 출력 데이터를 센스 앰프를 거치지 않고 아날로그 연산기를 통해 바로 처리하므로 SRAM과 프로세서 기반 PIM 구조의 가능성을 제시함

<그림 31> University of Illinois, Urbana-Champaign의 SRAM과 프로세서를 이용한 PIM (출처: ICASSP 2015)

- UCSB(University of California, Santa Barbara) 팀은 차세대 메모리인 ReRAM을 이용해서 PIM을 개발하고자 하는 연구를 ISCA 2016에서 발표함

- ReRAM은 두 개의 금속전극 사이에 절연막을 삽입한 매우 간단한 구조의 메모리 소자로서 전기적인 신호에 따라 저항이 크게 변화하는 원리를 이용한 차세대 비휘발성 메모리로서, 저항비 변화를 통해 간단하게 곱셈을 구현할 수 있음

- ReRAM은 기존의 낸드 플래시보다 속도가 10 배 이상 빠르며, 전력 소모를 30% 가까이 줄일 수 있으므로 크게 주목받고 있지만 아직은 기반 기술이 확립되지 않고 있음

<그림 32> University of California, Santa Barbara에서 개발한 DNN을 위한 ReRAM 기반의 PIM 구조 (출처: ISCA 2016)

- Toshiba에서도 최근 A-SSCC 2016에서 SRAM과 프로세서를 하나의 단위로 구성하는 PIM을 발표하였음

- 입력 파라미터의 값을 이진화하여 최소한의 정확도로 연산 복잡도 및 인지 정보 처리에 필

요한 데이터를 최대한 줄인 BNN(Binarized Neural Network)을 이용하여 외부 메모리 접근을 최대한 줄였으며, 내부 메모리 대역폭은 SRAM과 프로세서의 PIM 구조를 통해 확장함

- 뉴런의 시냅스 연결 간 연산은 타임 도메인 네트워크를 통해 함께 처리하는 TDAMS (Time-Domain Analog-digital Mixed-Signal)를 이용하므로 최대한 면적 효율적으로 처리 할 수 있도록 하고 아직 기반 기술은 확립되지 않았으나 에너지와 면적 효율적인 ReRAM을 이용한 PIM의 가능성도 제시함

<그림 33> Toshiba의 SRAM 혹은 ReRAM 기반의 PIM

(출처: A-SSCC 2016)

□ (초저전력 빅데이터 저장 솔루션) 인공지능 처리를 위하여 대용량의 데이터 처리를 효율적으로 하기 위한 DRAM, 낸드플래시등의 메모리 저장 솔루션 시장이 급속하게 확대됨에 따라서, 글로벌 기업들 대규모 투자를 통하여 시장 장악력을 확대하고, 차세대 메모리 솔루션을 원천 기술 개발을 경주하고 있음

- 인텔은 Altera를 \$16B에 인수한 이후에 Micron과의 합병을 통한 메모리 제품 및 솔루션 역량을 강화 시도

- 3D Xpoint 기술 개발을 위하여 Micron과 협력하고 있으며 차세대 CPU-메모리 통합 시장을 위해 Micron 인수를 통한 메모리 및 솔루션 확보에 적극적

- Marvell, PMC, NGD Systems 등 낸드플래시 저장 솔루션 전문회사의 성장으로 SATA, PCIe, eMMC 등의 제품 개발에 필요한 SoC 솔루션 제공

- Marvell은 6Gbps SATA, PCIe 용 SoC 솔루션을 개발하여 OCZ 등에 납품한 바 있으며, 최근에는 eMMC 5.0을 지원하는 모바일 솔루션을 개발

- PMC-Sierra는 NVMe SSD, SAS SSD 등의 개발에 필요한 저장 솔루션을 개발하였으며, 2016년초 \$2.5B에 Microsemi에 인수된 바 있음

- NGD Systems는 미국 정부 지원을 받아 스마트 스토리지 (in-situ processing) 제품을 개발, 빅데이터, 클라우드 응용에 적용

- Pure Storage, Violin Memory, Diablo Technology, Microsemi, Foremay, Kaminario, BiTMICRO, Memblaze, Tegile Systems, Virtium, Numbus Data Systems, Netlist, Viking,

SolidFire, Radian Memory, Nimble, Super Talent Technology, Kingston, V&G, EMC, IBM, Mangstor, Primary Data, Avere Systems, Memoright, Avant Technology, Fusion-io 등 낸드플래시 저장 솔루션 전문회사가 성장하고 있음

- 대만에서는 Phison, Silicon Motion, Innodisk 등은 자국 내 메모리 반도체 사업이 퇴보되고 있음에도 불구하고, 낸드플래시 저장 솔루션 업체로 성장

- Phison은 USB 드라이브, CF 카드, SD 카드 등에 관련한 메모리 솔루션을 개발하였으며, 최근 eMMC, uSSD, BGA SSD 등 다양한 형태의 솔루션 개발

- Silicon Motion은 SLC, MLC, TLC 등 다양한 낸드플래시 저장 솔루션을 개발하였으며, 최근 인텔 등과의 협력을 통하여 다양한 개인용 저장장치 제품을 제공 있음

- 중국에서는 최근 메모리 반도체 산업에 대한 투자를 시작한 이후, Waitan, Cactus, Renice와 같은 저장 솔루션 전문 업체를 발굴하여 지원

- Waitan은 중국 상하이에 기반을 둔 저장 솔루션 전문 업체로 국방, 항공, 산업용 응용을 위한 제품을 개발

- Cactus는 홍콩에 본사를 가지고 있으며, 산업용 제품에 필요한 저장 솔루션을 개발하여 제공하고 있으며, 국내 NovaChips와 같은 SSD 제품 개발 업체와 협력 관계를 구축

- Renice Technology는 보안, 암호화 기능이 강화된 저장 솔루션 개발 회사이며, 중국 선전에서 SATA 및 USB 3.0용 솔루션 기술 개발

- 일본에서는 낸드플래시 메모리 세계 2위 도시바는 eMMC, SSD 뿐만 아니라, 하드디스크와 저장 솔루션이 결합된 하이브리드 저장장치 개발에 집중

- 유럽에서는 Hyperstone, DensBit 등 패리스 기업 중심으로 저전력 저장 솔루션 개발

- 독일의 Hyperstone은 저전력 응용에 최적화된 저장 솔루션 전문회사로 SSD, Disk-on-Module, Disk-on-Board, eMMC 등 다양한 제품의 솔루션을 개발

- 최근 인텔 등과의 협력을 통하여 다양한 개인용 저장장치 제품을 제공하고 있음

- 국내에서는 메모리반도체 제조사가 중심이 되어, 시장 규모가 큰 제품 위주로 기술 개발을 하고 있으며, 최근 중소중견 기업을 중심으로 해외 시장을 겨냥한 저장 솔루션 개발을 진행

- 삼성전자, SK하이닉스 등은 저장 솔루션을 자체적으로 개발하여 상용화하고 있으나, SSD, enterprise, 모바일 등 대형 시장 위주의 저장 솔루션 제품 개발에 집중하고 있으며, 일부 차세대 제품에 대해 기술 개발 추진

- TLi, The AIO, NovaChips 등은 모바일 저장 솔루션과 특수 목적의 SSD 개발하고 있으며, 중국 등 해외시장을 중심으로 제품 판매를 가속화

- PADU는 서버 시스템에 적용 가능한 스토리지 제품에 대해 저장 솔루션을 개발하고 있으며, 국내외 서버 시장을 개척 중

- (CMOS 기반 신경세포모방 회로 기술) 현재 CMOS 공정 기술을 사용하여 SRAM, floating gate 등을 시냅스로 활용

- CMOS 기반 SRAM은 대량 생산에 용이하고 높은 신뢰성을 가지는 메모리 장치이며, 저장하

는 데 있어 주기적으로 초기화 작업이 필요 없고 접근 속도가 매우 빨라 실제 캐시 장치로 널리 사용되는 회로이지만 이진법(0 또는 1)으로 저장되기 때문에, 단위 면적 당 저장용량이 작으면 전력 소모가 크다는 단점을 지님

- 반면에 floating gate는 multi-level로 데이터를 저장할 수 있으며, 전력이 차단 되도 데이터 값을 유지 할 수 있는 비휘발성 특징을 가지지만, SRAM에 비해 신뢰성이 떨어지며 읽고/쓰기 방법이 간단하지 않는 문제점을 가짐

<그림 34> SRAM 타입의 CMOS 시냅스

(P.A. Merolla et al., Science, vol.345, p.668, 2014)

<그림 35> Floating gate 타입의 CMOS 시냅스(J. Hasler et al., Front. Neurosci., 10 September 2013)

- CMOS 기반의 뉴런은 근사 또는 통계적인 특성을 이용한 심층 인공 신경망 뉴런과 실제 뉴런의 동작을 모사한 스파이킹 인공 신경망으로 구분 할 수 있으며, 적용되는 모델에 따라 다양한 뉴런이 존재하며 대표적인 뉴런들의 특성을 다음 표로 정리함

| Deep Neural Network |         |      |                                                                  |

|---------------------|---------|------|------------------------------------------------------------------|

| Classes             | Model   | Year | Characteristics                                                  |

| Approximation       | Sigmoid | 1990 | Piece-wise linearization, trade off with performance and area    |

| Stochastic          | Sigmoid | 2000 | fault tolerance, compact trade off computation time and accuracy |

| Spiking Neural Network |                |      |                                                              |

|------------------------|----------------|------|--------------------------------------------------------------|

| Classes                | Model          | Year | Characteristics                                              |

| Sub-threshold          | Thalamic relay | 2009 | Conductance-based, thermodynamically equivalent, compact     |

|                        | H-H model      | 1998 | Conductance-based, biologically realistic, not compact       |

|                        | Tau-cell       | 2000 | Log-domain, modular                                          |

|                        | LLN            | 2004 | Log-domain, cubic two-variable model, low power, compact     |

|                        | DPI            | 2004 | Current-mode, exponential adaptive model, low power, compact |

| Spiking Neural Network |                     |      |                                                                 |

|------------------------|---------------------|------|-----------------------------------------------------------------|

| Classes                | Model               | Year | Characteristics                                                 |

| Above-threshold        | Quadratic I&F       | 2008 | Voltage-mode, accelerated-time, low power, compact              |

|                        | Current-controlled  | 2006 | Voltage-mode, conductance-based, accelerated time               |

|                        | Switched-Capacitor  | 2009 | Mihalas-Niebur adaptive threshold model, discrete time, modular |

|                        | Digitally modulated | 2006 | Basic I&F model, discrete time, low mismatch                    |

□ (신경세포모방 소자 기술) 멤리스터, 스피нт로닉스 등의 이미징 디바이스를 뉴런 또는 시냅스로 사용

- 스피нт로닉스 또는 멤리스터를 이용하여 인간 뇌 신경세포인 뉴런의 동작을 모사함. 기존 CMOS를 통해 만든 뉴런 회로에 비해 훨씬 적은 전력으로 빠르게 동작이 가능

- RRAM, PRAM, FeRAM 등 메모리 소자들을 뇌의 시냅스 세포의 동작과 유사하게 만들기 위한 연구가 진행 중. 외부 전압 펄스에 의한 각 소자의 저항이 순차적으로 바뀌는 현상을 이용

- 신경세포 모방소자를 채용한 대규모 하드웨어 기반 인공신경망 전용 반도체는 많은 양의 뉴런과 시냅스를 병렬 구조로 에너지 효율적으로 구성하는 방법을 주로 연구함. 다수 연구 그룹이 이미 실리콘 소자를 이용하여 초기 형태의 하드웨어 기반 인공신경망 전용 반도체 개발 완료 단계에 진입했으며, 다중 사물인식 시스템이나 기존의 슈퍼컴퓨터를 이용하여 수행하던 두뇌 동작 시뮬레이션 등의 활용분야에 적용됨.

## □ Emerging device 뉴런

### ○ Straintronic spin device

- Straintronic spin neuron은 전압에 의한(여기서 전압은 입력전압의 가중합) 기계적인 변형(strain)을 통하여 Magneto Tunneling Junction(MTJ)을 스위칭 하여 뉴런동작을 구현함

- 이는 회전 편광 (spin-polarized) 전류를 통해 회전 전달 토크를 정보로 사용하는 기존 방식과 비교할 때 더 적은 에너지를 소모하고, 빠른 동작 특성을 가짐

<그림 36> straintronic spin 뉴런의 형태

(Ayan K. Biswas, et al. Nanotechnology, 2015.)

### ○ Memristive Oscillation device

- Oscillatory Neural Network(ONN)는 oscillator를 이용해 신경망을 모사하는 뉴로모픽 기술임

- 기존 CMOS를 통해 만들어진 oscillator 일반적으로 많은 전력 소모와 면적을 차지하므로 수 많은 시냅스를 가진 실제 신경망을 모사하는데 적절하지 않음

- Memristive Oscillation device는 산화물 기반의 RRAM 형태의 oscillator로 기존 방식의 Oscillator에 비해 훨씬 적은 전력으로 빠르게 동작하므로 진동 신경망 회로(ONN)를 구현하는데 적합한 기술임

<그림 37> ONN회로를 사용한 패턴인식

(A.A. Sharma, VLSI Technology Symposium, 2015.)

## □ Emerging device 시냅스

### ◦ Resistive RAM(RRAM)

- 주로 멤리스터(Memristor)로 불리우는 저항 메모리(RRAM)는 외부 전압 펄스를 인가하면 저항이 변하는 특성을 가졌음

- Multi-value 데이터를 저장할 수 있는 아날로그 시냅스로 적용됨. 2007년 처음 HP에서 멤리스터를 이용한 자기 조직화(self-organized) 컴퓨팅의 가능성을 확인 하였으며, 이를 통해 패턴인식 시스템의 구현 가능성을 시뮬레이션을 통해 검증하였음

- 2010년 미국 미시간 대학에서는 Si/Ag 복합물질을 이용하여 멤리스터를 구현하였고, 이를 바탕으로 spiking time dependent plasticity(STDP)의 시냅스 기능을 선보임

- 최근에는 미국의 UCSB 대학에서는 CMOS 기술과 반도체/나노와이어/분자 집적회로 (molecular integrated circuits)를 결합한 CMOL 기술을 네이처지에 기고함

- CMOL을 통해 기존 CMOS 기술과 two-terminal의 멤리스터를 함께 구현할 수 있는 가능성 을 보임

<그림 38> CMOL 회로 구현 형태

(M. Prezioso, et al., Nature 521, pp. 61–64, May 2015)

### ◦ Phase Change RAM(PCM)

- 상 변화 메모리(PCM)는 외부 전압 펄스를 통해 물질의 비정질 상태와 다결정질 상태 간의 저항 변화를 이용하는 비휘발성 메모리 소자임

- 저항 변화를 정교하게 진행하면, multi-value 데이터를 저장할 수 있는 아날로그 시냅스로 활용됨

- 상 변화 메모리는 멤리스터와 같은 2단자 소자로 크로스 바 구조의 array가 구현이 가능하며 전력 소모 또한 적어 뉴로모픽 시스템의 시냅스 소자로 사용됨

- 2011년 미국의 스탠포드 대학에서는 GST PCM 크로스바 array 소자를 이용하여 spiking time dependent plasticity(STDP)의 시냅스 기능을 선보임

- 그해 IEDM에서 앞선 소자를 이용한 associative 메모리 기능의 모사가 가능하다는 것을 선보임

- 2011년 프랑스의 LETI에서는 상변화 메모리 소자를 시냅스로 사용하여 패턴인식 시스템을

## 시뮬레이션으로 구현함

<그림 39> 상변화 메모리 소자를 시냅스로 사용한 패턴인식 시스템

(M. Suri et al, et al., IEDM, Sep, 2011)

### ○ Ferroelectric RAM

- Ferroelectric RAM은 2단자 형태의 강유전막(Ferroelectric film)에 외부 전압 펄스를 인가하면서 저항이 바뀌는 특성을 이용해 비활성 아날로그 메모리로 활용됨

- 강유전막 메모리는 전자의 터널링에 비해 높은 스위칭 속도와 저전력, 100nm 미만의 사이즈를 갖는 특징을 갖지만, 물질의 계면 상태 문제 및 강유전막 내부 확산 등과 같은 불완전한 현상들로 인해 정확한 특성 분석이 어렵다는 문제점을 지님

- 2013년 파나소닉은 CMOS 디지털 회로에 3T-강유전막 메모리를 제작하여 이미지를 아날로그 방식으로 처리할 수 있는 영상 시스템을 발표하였는데, 소비 전력이 기존 디지털 시스템에 비해 1/10 정도이며, 강유전체 성장기술과 디지털-아날로그 혼성 신호처리기술이 핵심임

<그림 40> CMOS회로와 강유전체 맴리스터를 결합한 구조

(Y. Kaneko, et al., VLSI Technology Symposium, 2013)

### □ 대규모 뉴로모픽 시스템

- 대규모 뉴로모픽 시스템은 많은 양의 뉴런과 시냅스를 병렬 구조로 에너지 효율적으로 구성하

는 방법을 주로 연구함

- 다수 연구 그룹이 이미 실리콘 소자를 이용하여 초기 형태의 뉴로모픽 프로세서를 개발 완료 단계에 진입했으며, 다중 사물인식 시스템이나 기존의 슈퍼컴퓨터를 이용하여 수행하던 두뇌 동작 시뮬레이션 등의 활용분야에 적용됨.

- Institute for Neural Computation(INC) in University of California, San Diego

- Integrated and Fire Array Transceiver 칩(IFAT,2004)

- 가변구조 형(reconfigurable)의 2400개의 뉴런으로 구성된 인공신경망을 하드웨어로 구현 하였으며, 실시간으로 동작함

- IFAT의 내부적인 계산은 아날로그 값으로 수행되며, 출력 및 시스템 컨트롤은 디지털로 동작함

- 시냅스의 가중치 값은 off-chip의 RAM(look-up table)에 저장되었으며, Address Event Representation (AER)을 이용하여 IFAT의 뉴런과 off-chip 하드웨어 간에 통신함

- Hierarchical AER I&F Array Transceiver 칩(HiAER IFAIT,2012)

- $256 \times 103$ 개의 스파이킹 뉴런과  $256 \times 106$ 개의 가변구조 형태의 conductance 기반의 시냅스로 시스템을 구성함

- 자일링스 사의 Spartan-5 FPGA을 이용하여 IFAT 칩들을 tree 아키텍처로 구현함

<그림 41> Hirerachical AER I&F Array 트랜시버

(P. Jongkil, et al., IEEE ISCAS2012, 2012)

- Neurogrid in Stanford University

- Neurogrid

- 연구목표 : 두뇌가 동작하는 방법을 연구하기 위한 하드웨어 시뮬레이션 툴(tool)

- NeuroCore는  $256 \times 256$ 의 4b 시냅스 어레이와 quadratic Integrated and Fire 뉴런으로 구성됨

- 180nm의 CMOS 공정을 이용하여 비동기화식으로 동작하는 스파이킹 인공신경망을 구현

- NeuroCore를  $4 \times 4$ 의 트리(tree) 아키텍처를 이용하여 백만개(one million)의 뉴런과 단위 뉴런당 7980개의 시냅스를 연결할 수 있으며 3.1mW를 전력을 소모

<그림 42> Brains in Silicon 그룹의 NeuroGrid

(B. V. Benjamin, et al., Proceedings of the IEEE, 2014)

◦ Digital Multi–Neurosynaptic Core in IBM

- True North

- 256개의 디지털 leaky Integrated and Fire 뉴런과  $256 \times 256$  시냅스 어레이의 연산장치 4096개로 구성됨. 총 백만개의 뉴런과 2억5천만개의 시냅스를 구현함

<그림 43> IBM의 True North 구성

(P.A. Merolla, et al., Science, 2014)

- 삼성의 28nm 미세 공정을 이용하였으며, 단위  $\text{cm}^2$  당 100W를 소모하는 일반 CPU에 비해 True North는 20mW만 사용함

- NeuroCore를  $4 \times 4$ 의 트리(tree) 아키텍처를 이용하여 백만개(one million)의 뉴런과 단위 뉴런당 7980개의 시냅스를 연결할 수 있으며 3.1mW를 전력을 소모

- 어떠한 수정 없이도 offline 러닝, convolution neural networks, liquid state machine, Restricted Boltzmann machine, hidden markove model, support vector machine, multimodal classification등의 다양한 기계학습이 적용 가능함

- 초당 30 프레임의  $240 \times 400$ 개의 픽셀로 구성된 컬러 이미지의 비디오의 움직이는 물체 5가지(사람/자전거/승용차/버스/트럭)를 실시간으로 판단하는 multi–object recognition하는 동작을 시현함

<그림 44> 실시간으로 동작하는 다중 물체 인식 시스템

(P.A. Merolla, et al., Science, 2014)

- FACETS and Brain Scale Project in University of Heidelberg

- High-Input Count Analog Neural Networks Chip(HICANN)

- HICANN 연산장치는 180nm 공정을 사용하였으며, 512개의 leaky integrated and fire 뉴런과 114688개의 4b의 floating gate 시냅스로 구성됨

- 384개의 HICANN 연산장치를 집적화 시킨 20cm의 단일 실리콘 웨이퍼 20개를 이용하여 4백만개의 뉴런과 8억 8천개의 시냅스를 하나의 시스템으로 구현함

- 단일 뉴런당 14336개의 시냅스가 연결가능하며 실제 생체학적 뉴런보다 만배 빠른 동작 속도를 보임

<그림 45> University of Heidelberg의 HICANN 연산장치와 웨이퍼 scale 모듈

(J. Schemmel, et al., IEEE IJCNN, 2008)

- SpiNNaker Project in University of Manchester

- SpiNNaker

- 유럽의 Human Brain Project의 일환으로 기존의 접근 방법의 Integrated and Fire 뉴런이 아닌 130nm 공정을 이용한 18개의 ARM968 프로세서와 128M 바이트의 SDRAM을 이용하여 뉴로모픽 시스템을 구현

- 대량의 병렬처리 시스템(massive parallel system) 디자인 되었으며, event가 발생 시 동작하는 방법으로 연산을 수행함

- Standard STDP, spike-pair STDP, STDP with time-to Spike 등과 같은 학습 방식을 사용하여 생체 뉴런의 행위 동작을 시뮬레이션하기 위해 설계됨

<그림 46> University of Manchester의 SpiNNaker 연산장치

(S. B. Furber, et al., Proceedings of the IEEE, 2014)

- Institute of Neuroinformatic in University of Zurich and ETH Zurich

- ROLLS neuromorphic processor

- 가변구조 형의 온라인 학습 스파이킹 인공신경망 시스템(Reconfigurable Online Learning Spiking, ROLLS)

- 180nm 공정을 사용하여 256개의 adaptive integrated and fire 뉴런과 133120개의 시냅스를 구현함

- Short Term Potential(STP)시냅스, Long Term Potential(LTP)시냅스 그리고 linear 시냅스로 구성됨

- 안구의 황반부를 모델링한 Dynamic Vision Sensor(DVS)와 convolution neural networks로 구성된 ROLLS를 이용하여 물체를 인식하는 시스템을 구현함

<그림 47> ROLLS 뉴로모픽 프로세서와 물체인식 시스템

(N. Qiao, et al., Frontiers in Neuroscience, 2015)

- (국내 연구개발 동향) 국내에서 다음과 같이 대학 연구소 중심으로 연구가 진행되고 있음. 우리나라의 신경세포 모방소자 연구분야는 미국, 유럽과 비교하여 비교적 늦게 시작되었기 때문에 차세대 소자를 이용한 소자 개발 연구가 활성화 되고 있음

<표 7> 신경세포 모방소자 국내 연구 개발 동향

| 연구기관        | 연구내용                                                                                                                                                | 특징                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 서울대         | <ul style="list-style-type: none"> <li>- Charge-trap 메모리를 이용 신경세포를 모방하기 위한 소자 연구</li> <li>- Floating-body MOSFET 구조를 이용하여 신경세포 모방 소자에 적용</li> </ul> | <ul style="list-style-type: none"> <li>- 신경모사 시스템에 필요한 뉴런/시냅스 소자 및 회로 구현</li> </ul>                                                |

| KAIST       | <ul style="list-style-type: none"> <li>- 기계식 방식 이용 고에너지 효율 반도체 소자의 특성 및 성능 연구</li> </ul>                                                            | 나노미터 수준의 집적도 구현                                                                                                                    |

| POSTECH     | <ul style="list-style-type: none"> <li>- 멤리스터 이용 신경세포 모방소자 연구</li> </ul>                                                                            | <ul style="list-style-type: none"> <li>- 패턴인식용 뉴로모픽 하드웨어에 적용</li> </ul>                                                            |

| 서강대         | <ul style="list-style-type: none"> <li>고에너지 효율 반도체 소자 연구</li> <li>삼차원 집적 재구성 가능 논리 회로 구현</li> </ul>                                                 | <ul style="list-style-type: none"> <li>- 인공지능 반도체 구현을 위한 에너지 효율, 삼차원 집적 공정, 재구성 가능 논리 회로 개발</li> </ul>                             |

| GIST        | <ul style="list-style-type: none"> <li>- CMOS/멤리스터 이용 뉴로모픽 회로 구현</li> </ul>                                                                         | <ul style="list-style-type: none"> <li>- 이미지 센서를 이용한 패턴 인식용 뉴로모픽 하드웨어 개발</li> </ul>                                                |

| 서울시립대       | 고에너지 효율 반도체 소자 연구                                                                                                                                   | <ul style="list-style-type: none"> <li>- 새로운 절연 물질을 이용하여 반도체 소자의 에너지 효율 향상</li> </ul>                                              |

| 삼성전자        | 차세대 메모리 및 집적도 향상 기술 연구                                                                                                                              | <ul style="list-style-type: none"> <li>- 2011년 Grandis 인수</li> <li>- 2014년 MRAM Innovation 프로그램을 통하여 전세계 다양한 연구기관과 공동연구</li> </ul> |

| SK<br>하이닉스  | 차세대 메모리 및 집적도 향상 기술 연구                                                                                                                              | <ul style="list-style-type: none"> <li>- 도시바, HP 등과 공동연구</li> </ul>                                                                |

| 삼성<br>종합기술원 | <ul style="list-style-type: none"> <li>- CMOS 기반 신경세포 모방 소자기술 연구</li> </ul>                                                                         | <ul style="list-style-type: none"> <li>- EU의 FACET 프로그램과 협력</li> </ul>                                                             |